-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

トピックの詳細

マイクロチップとは

マイクロチップは、ドーパント、酸化剤、金属を用いて加工した小さく平らな半導体材料で構成された電子デバイスです。これを用いて回路内で接続されたトランジスタ、ダイオード、抵抗器、コンデンサなどの電子コンポーネントを製造します。

マイクロチップは、以下の名称でも呼ばれています。

- 集積回路(IC)

- コンピュータチップ

- 半導体

- チップ

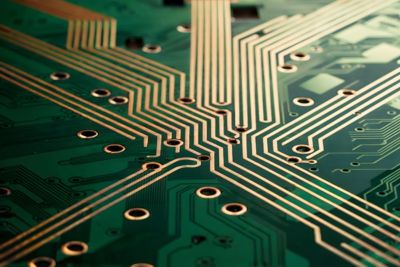

集積回路は、単一のモノリシックデバイスであり、はるかに小型で、消費電力が大幅に少なく、非常に低コストで大量生産できるため、ワイヤ配線やプリント回路基板(PCB)で接続された個別コンポーネントのアセンブリに取って代わりました。

半導体材料は1821年にThomas Johann Seebeckによって発見され、1947年にWillam Shockleyによって初めての稼働する半導体トランジスタが作成されました。1959年には、Robert Noyceによってコンポーネントとすべてのインターコネクトが1つのデバイスに統合されました。この発明の鍵となったのは、フォトリソグラフィを使用して材料を1層ずつ正確に堆積および除去する平坦な製造プロセスでした。

集積回路は、玩具から深宇宙探査機まで、さまざまなデバイスのエレクトロニクスを提供する現代の生活に不可欠な要素です。2023年のマイクロチップの全世界での売上高は5,269億ドルでした。また、同年のコンピュータ以外でのチップ使用率もさらに増加し、その内訳は32%が通信、17%が自動車分野、14%が産業機器、11%が消費者向けエレクトロニクス製品、そして25%がコンピューティングでした。

IC内のトランジスタ数が2年ごとに2倍になるというムーアの法則に則り、回路の複雑さは増し、コンポーネントのサイズがますます縮小しているため、チップの世代ごとにマイクロチップの設計と製造はより困難になっています。

チップ上の個々の素子の一般的なサイズは「フィーチャーサイズ」と呼ばれ、ナノメートル(nm)単位(10億分の1メートル単位)で測定されます。現在、半導体メーカーは14nm、10nm、7nm、5nm、および3nmプロセスを使用しており、2nmテクノロジーも登場し始めています。米粒の長さが500万ナノメートルであることを考えれば、その小ささが理解できるでしょう。

2023年、研究者たちはこれまでで最多となる1.2兆個のトランジスタを搭載したマイクロプロセッサを開発しました。また、2024年にIntel社が発売したCPUでは、1つのチップに1億個以上のトランジスタが搭載されています。

代表的なマイクロチップの要素

集積回路は、半導体材料(通常はシリコン)を重ねた積層として製造されます。マイクロチップを構成する最も一般的な要素を以下に挙げます。

- シリコン基板: 他の材料を除去または堆積するか、結晶物質をドーピングすることで他の層が堆積される純シリコン結晶基層。

- 層: 電子回路は、個々の層の上に作成されます。フォトリソグラフィ、エッチング、および堆積で層を加工し、目的のコンポーネントやインターコネクトが生成されます。一部の層は、電気絶縁体としても機能します。

- ビア: 層間で電気信号を伝送するために使用される伝導帯(通常は円筒形)。

- コンポーネント: 目的の回路を構成する電子デバイス。多くのICで、これらはトランジスタ、コンデンサ、ダイオード、抵抗器、場合によってはインダクタで構成されています。

- インターコネクト: コンポーネント間またはビアに電気を伝導する層上の金属化されたパス。

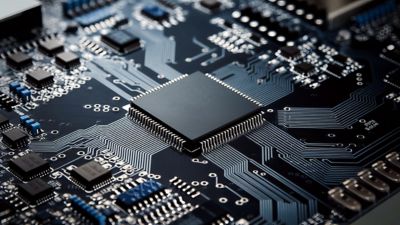

- パッケージング: 完成すると、ICは半導体パッケージと呼ばれるアセンブリ内に配置されます。このパッケージは、繊細なシリコンチップを保護して絶縁し、複数のチップを接続でき、チップをより大きな電子回路に接続する方法をもたらします。

マイクロチップの製造方法

マイクロチップ製造には、3つのステップがあります。各ステップは、コストを最小限に抑え、品質を確保し、効率を最大化するために高度に最適化および自動化されています。各ステップによってコンポーネントのサイズ、形状、間隔が決まるため、ICを設計するエンジニアは製造プロセスを十分に理解する必要があります。

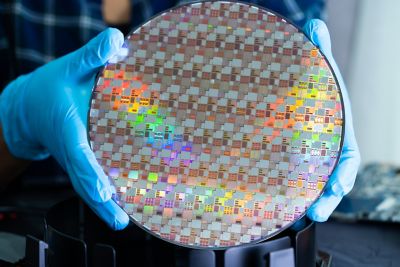

ステップ1: ウェハ製造

半導体製造の最初のステップは、ブランクシリコンウェハの製造です。この工程は、半導体材料(通常は純シリコン)の円筒形の単結晶インゴット(「ブール」と呼ばれる)を成長させることから始まります。このブールを薄いウェハにスライスし、機械加工によって平らな表面を形成して、機械加工による損傷を除去するために化学的なエッチングを実行し、研磨します。電子ウェハの直径は、一般的に100~450mmです。最も一般的なサイズは、幅300mm、厚さ755µmです。

ステップ2: 製造

回路は、そのすべてのコンポーネントとインターコネクトとともに、「ファブ」と呼ばれる半導体製造施設で作成されます。回路の各層およびトポロジーは、高度に制御された一連の工程で作成されます。ロボットを使用して、複数のウェハをまとめて機械から機械へと移動させます。ほとんどのチップ製造プロセスでは、層ごとに以下の手順を実行します。

- 層を完全に覆うように二酸化ケイ素の層を成長させます(「不動態化」とも呼ばれる)。

- フォトレジスト剤を塗布します。

- フォトレジスト層に紫外線を照射して、目的のジオメトリパターンを焼き付けます。このフォトレジスト層を現像すると、感光した箇所の材料が除去されます。これは「フォトリソグラフィ」と呼ばれます。

- 化学物質(通常は強酸)を使用して、フォトレジストが除去された酸化膜を除去します。これは「エッチング」と呼ばれます。

- 未現像のフォトレジスト剤を取り除きます。

- 層のドーピングが必要な場合は、結晶構造に汚染物質をイオン注入することで、トランジスタやその他のコンポーネントに望ましい半導体挙動が得られます。

- 他の材料については、さまざまな化学気相成長法または蒸着法を用いてインターコネクト、ビア、その他のコンポーネントが作成されます。

ステップ3: パッケージング

各層が作成され、ウェハの洗浄やテストが完了すると、「ダイ」と呼ばれる個々のチップに切断されます。1つまたは複数のダイをボンディングして構造に取り付け、ICを用途に応じて異なる材料にカプセル化します。単一のチップのみが含まれているパッケージもありますが、現在は複数のダイを1つのパッケージにまとめることが多くなっています。

マイクロチップのタイプと用途

集積回路のタイプと用途は年々増えています。初期に登場したICの多くは、単一の機能のみを実行しました。しかし、製造技術と設計ツールが向上するにつれて、多数の機能を備えたチップに移行しています。

その一例は、さまざまな用途に対応するために、1つのデバイスに複数のタイプのチップを組み合わせたスマートフォンです。5G電波およびGPS用の高周波(RF)チップ、カメラ用の光電子チップ、ディスプレイ用のLEDチップ、処理装置用のデジタルIC、加速度計用のマイクロ電気機械システム(MEMS)チップ、そして極めて多くの用途で検出、制御、変更を行うための各種の集積回路が搭載されています。

チップのタイプは、伝送する信号によって分類できます。

アナログ集積回路

アナログ信号は、高電圧または低電圧信号だけでなく、連続する電圧範囲にわたって電圧を伝送します。アナログICは、信号の増幅やミキシング、そして周波数に基づくフィルタリングを行うために用いられます。アナログICの周波数と電力はさまざまで、周波数と電力が高くなると、設計上の大きな課題が生じます。

アナログICの一般的な用途は以下のとおりです。

- 光学、熱、およびオーディオセンサー

- パワーマネジメント回路

- オペアンプ

- オーディオおよびビデオ信号処理

- 無線通信や光信号処理を含む通信

- RF回路

- 信号調整

- マシンコントローラ

デジタル集積回路

デジタルICは、トランジスタで構成される数百万から数十億個のロジックゲートを含むロジックデバイスです。固定クロック周波数で動作する信号は、ハイまたはロー、あるいはゼロまたは1として変調または測定されます。異なるロジックデバイスを組み合わせることで、最小限の消費電力で極めて複雑な計算を実行できます。

デジタルICの最も一般的な用途には以下のものがあります。

- ロジックICまたはプロセッサ

- マイクロプロセッサ

- マイクロコントローラ

- 特定用途向け集積回路(ASIC)

- メモリチップ

- フィールドプログラマブルゲートアレイ(FPGA)

- デジタルパワーマネジメントデバイス

- システムオンチップ(SoC)デバイス

- マルチダイチップ

ミックスドシグナル集積回路

一部の集積回路では、回路を組み合わせてアナログ信号とデジタル信号を処理し、2つの信号間を変換してミックスドシグナル集積回路を形成します。アナログ信号が検出または生成され、その信号の読み取り、作成、または変調に論理演算が必要な場合に使用されます。

ミックスドシグナルICの最も一般的な用途には以下のものがあります。

マイクロチップテクノロジーの今後のトレンド

マイクロチップはこれまでと同じように、より低コストで、より小さなサイズで、より多くの機能を備えた製品に向けて開発が進められるでしょう。製造技術が進歩すると、より優れた性能と新しい用途のための新しい機会も生まれます。

今後、電気エンジニアリングの設計とシミュレーションを推進するトレンドとしては、以下のようなものがあります。

ファブレス設計およびファウンドリへの移行

半導体業界では、企業が独自のICを設計して、チップ製造に特化したメーカーに製造を委託するモデルに移行してきました。この手法はファブレス設計と呼ばれ、契約メーカーはファウンドリと呼ばれます。こうしたモデルを採用することで、Apple社やQualcomm社などの企業は、自社の製造施設のための設備投資を行うことなく、革新的な新製品を設計できるようになりました。エンジニアは、使用するファウンドリの製造プロセスや基準に合わせて設計する必要があります。

より小さいフィーチャーサイズ

フィーチャーサイズは縮小し続けており、パワーインテグリティとシグナルインテグリティの問題が生じています。電気エンジニアは、これらの新しい機能を使用して設計するだけでなく、シミュレーションと設計のベストプラクティスを活用して問題を回避し、競争力を維持しなければなりません。

電子デバイスの複雑さと統合された機能

電子デバイスの設計者は、今後、より優れた機能をシングルチップで提供することを目指すことになります。モノのインターネット(IoT)デバイス、新しいソリッドステート長期ストレージ、GPUチップは、単一チップに新しい機能を搭載するだけでなく、それらの機能間の相互作用もさらに高度になる集積回路の例です。業界がテクノロジーを活用していく方向に合わせて設計を推進できるような設計ツールやシミュレーションツールが必要となっています。埋め込み型のマイクロチップのようなバイオメディカルエレクトロニクスも、1つのチップに複数の機能が必要とされる分野です。

クロック速度と周波数の上昇

性能に対する要求が高まり、RFテクノロジーが進歩するにつれて、デジタルICのクロック速度や、アナログ信号およびミックスドシグナルチップの周波数が上昇しています。どちらもシグナルインテグリティとパワーマネジメントの問題につながります。

エネルギー効率の向上による計算能力の向上

人工知能、暗号通貨のマイニング、IoTアプリケーションといったトレンドをサポートするために、ハイパフォーマンスコンピューティングによるデータセンターが増え続けており、さらに性能が向上したマイクロプロセッサに対する需要が高まっています。こうした分野によって、業界全体でFPGA、ソリッドステートハードディスクドライブ、メモリ、GPUを向上させ、高速なデータ転送であらゆるものを接続するために必要なチップを改善する取り組みが進められています。

計算以外の用途の拡大

自動車、消費者向けエレクトロニクス製品、産業用途でのマイクロチップの採用が増加する傾向は今後も続くでしょう。ほぼすべての製品が、ブロードバンド、センサー、コンピューティング能力に接続できるスマートデバイスとして設計され、マイクロチップが不可欠となります。

マイクロチップ設計におけるシミュレーション

マイクロチップ製造の複雑さと高いコストにより、プロトタイプ作製による設計は現実的ではありません。代わりに、エンジニアはシミュレーションによる仮想的なプロトタイプ作製を活用して、設計を推進し、性能を検証して、生産を開始する前に問題を特定して解決しています。シミュレーションは、パッケージングの設計や、チップを製造する半導体製造装置の最適化にも使用されています。

デジタルマイクロチップのためにシミュレーションを導入するには、まずRTL設計を用いて、抽象レベルでデジタル設計の論理機能を検証する必要があります。これには、Ansys PowerArtist™を使用したパワーマネジメントの調査が含まれます。このツールは、プロセスの早い段階で設計の電力ニーズを評価して、電力効率の高い設計を推進するのに役立ちます。

物理的な設計が完了すると、次にデジタルICのパワーノイズと信頼性解析で高く評価されているAnsys RedHawk-SC™を使用して、設計における電圧降下とエレクトロマイグレーションを評価することができます。

アナログおよびミックスドシグナルについては、Ansys Totem™をプロセスに導入して、パワーインテグリティと信頼性のサインオフを行えるようになります。このツールはエレクトロマイグレーションマルチフィジックスのゴールドスタンダードとして高く評価されており、最小3nmまでのすべての主要ファウンドリで認証されています。また、Ansys PathFinder-SC™と連携させて、静電放電を計算することもできます。

設計の最適化と検証が完了すると、パッケージングエンジニアはシミュレーションを使用してマイクロチップパッケージ全体のパワーインテグリティ、シグナルインテグリティ、ロバスト性を最適化できます。RedHawk-SCは、システムインパッケージ設計を含む大規模なマルチチップ構成を扱うために設計されたソフトウェアです。先端半導体パッケージング技術では、2.5Dおよび3D-ICアプローチを使用し、同一パッケージ内で複数のダイを組み合わせて接続しますが、こうした設計を検証して最適化するには、RedHawk-SCが最適です。

設計の電気的側面を解決した後、パッケージングエンジニアはAnsys Mechanical™やAnsys Icepak®ツールを使用して、構造の信頼性と熱マネジメントを解析できます。

関連リソース

さあ、始めましょう

エンジニアリング課題に直面している場合は、当社のチームが支援します。豊富な経験と革新へのコミットメントを持つ当社に、ぜひご連絡ください。協力して、エンジニアリングの障害を成長と成功の機会に変えましょう。ぜひ今すぐお問い合わせください。