主な機能

PathFinder-SCに搭載されたデータモデリング、抽出、および過渡シミュレーションエンジンは、ESD検証のためのエンドツーエンドソリューションです。シングルパス使用モデルは、業界標準の設計フォーマットを読み取り、ESDルールを設定し、電源ネットワークのRCを抽出し、ESDシミュレーションを実行して根本原因を解析し、修正と最適化のフィードバックをすべて1つのツールで提供します。

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

Ansys PathFinder-SCは、静電放電(ESD)に対する健全性と堅牢性を確保するためのIPおよびフルチップSoC設計の計画、検証、およびサインオフを支援する大容量ソリューションです。

Ansys PathFinder-SCは、デバイス帯電モデル(CDM)、人体モデル(HBM)、またはその他のESDイベントによってチップ故障を引き起こす可能性のある、設計上の問題の根本原因を特定します。大容量のクラウドネイティブアーキテクチャにより、数千ものコンピューティングコアを搭載して、フルチップの高速なターンアラウンドを実現できます。PathFinder-SCは、ESDサインオフのための抵抗および電流密度チェックについて、大手ファウンドリから認証されています。

PathFinder-SCに搭載されたデータモデリング、抽出、および過渡シミュレーションエンジンは、ESD検証のためのエンドツーエンドソリューションです。シングルパス使用モデルは、業界標準の設計フォーマットを読み取り、ESDルールを設定し、電源ネットワークのRCを抽出し、ESDシミュレーションを実行して根本原因を解析し、修正と最適化のフィードバックをすべて1つのツールで提供します。

ロレム・イプサムは、未知のプリンタがタイプのゲラを取り、それをスクランブルしてタイプ標本帳を作った、1500年代以来、業界標準のダミーテキストでした。それは5世紀だけでなく、生き延びてきました

静電放電と電流密度は、チップの実際の堅牢性と長期的な信頼性を決定する重要な要素です。これらは、製品の安全性と耐久性にとって重要です。

デバイスの破壊電圧とインターコネクトの寸法を下げると、サブ16nmプロセスでESDリスクが高まります。PathFinder-SCは、すべてのチップ設計で要求されるオンチップESDイベントの包括的な解析を提供します。

PathFinder-SCのフルチップ容量と効率化されたシングルパス使用モデルは、1回の解析で数百のドメインを同時に処理できます。これは従来のアプローチよりも大幅に高速で、結果を得るまでの時間を短縮し、パーティション分割によるエラーの可能性を低減します。

検出された問題は、PathFinder-SCのレイアウトベースの解析および根本原因検出テクノロジーを使用して迅速にデバッグできるため、時間を節約して市場投入までの時間を短縮できます。

PathFinder-SCには、RC抽出およびESDシミュレーションの実行から根本原因の解析、最適化フィードバックの提供まで、すべての機能が1つの製品に含まれています。RC抽出ツールが内蔵されているため、追加のライセンスや外部ツールは不要です。

PathFinder-SCは、当社の顧客数社によりシリコン相関が検証され、複数のファウンドリによって妥当性が確認されているため、精度が確保され、シリコンに関するリスクが低減されます。

ロレム・イプサムは、未知のプリンタがタイプのゲラを取り、それをスクランブルしてタイプ標本帳を作った、1500年代以来、業界標準のダミーテキストでした。それは5世紀だけでなく、生き延びてきました

Ansys PathFinder-SCは、ESDに対する健全性と堅牢性を確保するためのIPおよびフルチップSoC設計の計画、検証、およびサインオフを支援します。デバイス帯電モデル(CDM)、人体モデル(HBM)、またはその他のESDイベントによってチップまたはIP故障を引き起こす可能性のある設計上の問題を特定します。PathFinder-SCは大手ファウンドリから認証されており、インターコネクト寄生成分、HBM/CDM ESDシミュレーション、および抵抗チェックや電流密度チェックがESDサインオフのための精度を満たすことを保証しています。レイアウトベースのGUIにより、根本原因の迅速な検出とデバッグが容易になります。

PathFinder-SCは、エラスティックコンピューティングを可能にし、1億を超えるトランジスタのフルチップ解析を処理できるクラウドネイティブインフラストラクチャで設計されています。

フルチップおよび包括的なシングルパスESD解析、さらには数百のパワーモードを同時デバッグ

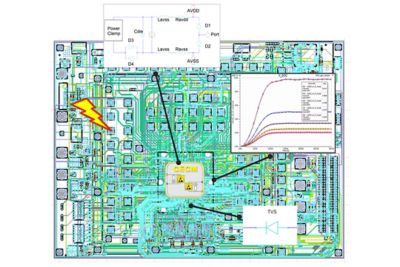

Ansys PathFinder-SCは、電源/グランドネットワークを介してザップ電流を伝播させ、レイアウトのボトルネックを特定することで、人体モデル(HBM)およびデバイス帯電モデル(CDM)のESDイベントを模倣します。パッドおよびインターコネクト経路への電流の注入をモデル化して、高ESD電流を処理できないピン-クランプ-ピン経路を特定します。

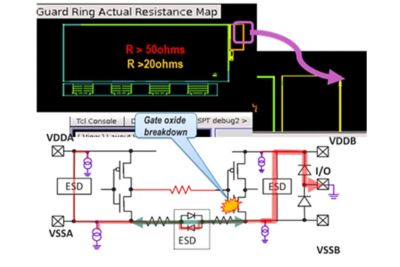

SPICEモデルとピコ秒分解能のTLP曲線を使用するAnsys PathFinder-SCの過渡シミュレーションでは、シリコン相関性の高い精度が提供されるため、設計上のリスクを最小限に抑えます。スナップバックを伴うクランプの場合、SPICEでは収束の問題が発生することがよくありますが、PathFinder-SCのシミュレーションエンジンは、スナップバックを処理し、ESDデバイストリガを正確にモデル化するようにカスタマイズされています。PathFinderの結果は、複数のファウンドリおよび顧客によってシリコン相関性が検証されています。

Ansys PathFinder-SCは、ESD故障につながる可能性のあるレイアウトの問題や接続の不均衡を特定します。たとえば、ESDクランプに接続されていないバンプや、電源/グランドに接続されていないクランプなどです。PathFinder-SCは、チップ上の任意の2つの関連ポイント間のすべての伝導路を横断することで、接続の堅牢性を検証し、ファウンドリまたはユーザーが指定した制限値に対して電気特性をチェックします。合格/不合格レポートは、レイアウトと相互に精査できます。

Ansys PathFinder-SCに搭載されたデータモデリング、抽出、およびシミュレーションエンジンでは、効率化されたシングルパスESD使用モデルが提供されます。ESDルールの設定、抽出およびESDシミュレーションの実行、根本原因の解析、修正および最適化フィードバックの提供などを単一ツール環境内で行えます。業界標準のデータフォーマット(GDS、DEF)を使用し、チェックするルールとパラメータを柔軟に指定できます。

Ansys PathFinder-SCは、1億を超えるインスタンスを含むIPおよび大規模SoCのESD健全性をチェックします。1回のシミュレーションで、数百の電源/グランド/信号ネットを処理し、抵抗および電流密度のチェックを実行します。フルチップのESDシミュレーションは、サイズに応じて数時間から1日で完了できます。PathFinder-SCは、超大規模な設計を処理するために、クラウドネイティブなエラスティックコンピューティングインフラストラクチャ上に構築されています。

信頼性の問題を回避するには、標準セルレベル、IPレベル、およびフルチップレベルで高電流ホットスポットを特定することが重要です。PathFinder-SCが備えるモデリング機能は、チップESDコンパクトモデル(CECM)に基づいており、標準セルからフルチップまで、あらゆるレベルで詳細なESD解析を可能にします。CECMには、PGモデル、クランプ装置、およびオプションの電流シグネチャが含まれます。この正確なモデリングは、あらゆる設計において最高の信頼性のニーズを満たします。

Ansys PathFinder-SCは、数千のCPUコアでクラウド実行するために設計されたSeaScapeビッグデータ分析プラットフォーム上に構築されており、コアあたりのメモリが少なくても、ほぼリニアな拡張性と非常に高い処理能力を発揮します。

Ansysは、障害を持つユーザーを含め、あらゆるユーザーが当社製品にアクセスできることはきわめて重要であると考えています。そのため、US Access Board(508条)、Web Content Accessibility Guidelines(WCAG)、およびVoluntary Product Accessibility Template(VPAT)の最新フォーマットに基づくアクセシビリティ要件に準拠するよう努めています。

エンジニアリング課題に直面している場合は、当社のチームが支援します。豊富な経験と革新へのコミットメントを持つ当社に、ぜひご連絡ください。協力して、エンジニアリングの障害を成長と成功の機会に変えましょう。ぜひ今すぐお問い合わせください。