主な機能

Ansys ExaltoのポストLVS RLCk抽出により、IC設計者は、以前は「解析するには大きすぎる」とされていた回路に対して、サインオフ段階で電磁結合と基板結合の効果を正確に予測できます。抽出されたモデルは回路図またはネットリストにバックアノテートされ、すべての回路シミュレータをサポートします。

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

Ansys Exaltoは、強力なポストLVS RLCk抽出ソフトウェアソリューションであり、IC設計エンジニアはサインオフ段階で電磁結合効果を正確に予測することができます。

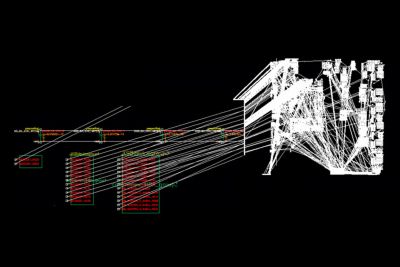

Ansys Exaltoは、ポストLVS RLCk抽出ソフトウェアソリューションです。IC設計者は、集中定数素子寄生成分を抽出し、電気的結合、磁気的結合、および基板結合の正確なモデルを生成することで、設計階層内の異なるブロック間の未知のクロストークを正確に把握することができます。ExaltoはほとんどのLVSツールに対応しており、お使いのRC抽出ツールを補完します。

Ansys ExaltoのポストLVS RLCk抽出により、IC設計者は、以前は「解析するには大きすぎる」とされていた回路に対して、サインオフ段階で電磁結合と基板結合の効果を正確に予測できます。抽出されたモデルは回路図またはネットリストにバックアノテートされ、すべての回路シミュレータをサポートします。

ロレム・イプサムは、未知のプリンタがタイプのゲラを取り、それをスクランブルしてタイプ標本帳を作った、1500年代以来、業界標準のダミーテキストでした。それは5世紀だけでなく、生き延びてきました

Nvidia、Ansys Raptor EM解析を適用してシリコン上の高速シリアルリンクのリスクを回避

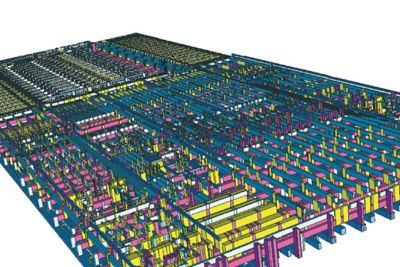

これまで「大きすぎて解析できない」とされていた大規模な複雑回路も、Exalto社のシリコンデバイス用EMモデリングの高速・大容量化により、手の届く範囲になりました。

最新のシリコンシステムにおけるRFおよび高速回路の急増により、信頼性の高いシリコンを実現するためには、電磁結合効果を正確にモデル化することが最重要課題となっています。しかし、電磁結合解析に適した正確な寄生モデルの生成は、従来のRC抽出よりもはるかに複雑です。また、これらのEMモデルの規模は、シミュレータにとって課題となっています。

Exaltoのこれまでにない容量により、非常に複雑なレイアウトを簡単に解析できます。独自のネットリスト縮退手法により、出力ネットリストは非常にコンパクトになり、シミュレーションの問題が軽減されます。これにより、コストが高くつく過大設計やガードバンディングによってこれまで回避されていた複雑な電磁相互作用を徹底的に解析できます。その結果、より信頼性の高い性能特性を有する小規模で安価な設計を得られます。

Exaltoは、通常のエクストラクタツールを補完し、すべてのLVSツールとシームレスに連携することで、既存の設計フローを強化します。

ロレム・イプサムは、未知のプリンタがタイプのゲラを取り、それをスクランブルしてタイプ標本帳を作った、1500年代以来、業界標準のダミーテキストでした。それは5世紀だけでなく、生き延びてきました

Ansys Exaltoは、集中定数素子寄生成分を抽出し、電気的結合、磁気的結合、基板結合の正確なモデルを生成することにより、ネットと階層ブロック間の未知のクロストークを捉えます。Exaltoでは、異なる階層レベル間のクロストークをモデル化し、回路図を変更せずに複数の「What-If」シナリオを実行できます。ポイント&クリック式のインターフェースを使用して、高感度RF回路内の複雑なカップリングと大きなデジタルバス/制御信号を容易に捉えることができます。独自のネットリスト削減手法により、出力ネットリストを90%以上削減します。Exaltoは、すべてのLVSツールに対応しており、設計の一部または全体に対してバックアノテーションされるSパラメータおよびRLCk寄生成分を用いてRC抽出ツールを補完します。

大規模で複雑なシリコン回路の電気的、磁気的、基板的な結合について、集中要素寄生を抽出し、正確なモデルを生成する。

Ansysは、障害を持つユーザーを含め、あらゆるユーザーが当社製品にアクセスできることはきわめて重要であると考えています。そのため、US Access Board(508条)、Web Content Accessibility Guidelines(WCAG)、およびVoluntary Product Accessibility Template(VPAT)の最新フォーマットに基づくアクセシビリティ要件に準拠するよう努めています。

エンジニアリング課題に直面している場合は、当社のチームが支援します。豊富な経験と革新へのコミットメントを持つ当社に、ぜひご連絡ください。協力して、エンジニアリングの障害を成長と成功の機会に変えましょう。ぜひ今すぐお問い合わせください。