主な機能

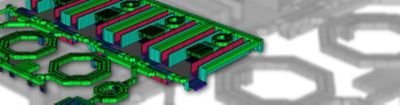

Ansys VeloceRFを使用して、複数のデバイスや伝送路が密にパッキングされたデバイスを合成し、最適化されたシリコンフロアプランを実現できます。詳細なレイアウトの前に、任意の数の誘導デバイス間のカップリングを解析することで、設計サイズを縮小し、ガードリングを削減または排除します。

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

Ansys VeloceRFは誘導デバイスの合成およびモデリングツールです。最小3nmという高度なノードをサポートし、主要なEDAプラットフォームと統合できます。

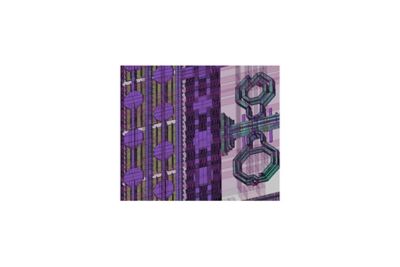

Ansys VeloceRFは、複雑なスパイラル形状のデバイスやTラインの合成とモデリングにかかる時間を大幅に短縮することで、設計サイクルを短縮します。インダクタやトランスのジオメトリをコンパイルするのに数秒しかかからず、モデリングと解析には数分しかかかりません。主要なEDAプラットフォームと統合され、テープアウト可能なレイアウトをインスタンス化します。

Ansys VeloceRFを使用して、複数のデバイスや伝送路が密にパッキングされたデバイスを合成し、最適化されたシリコンフロアプランを実現できます。詳細なレイアウトの前に、任意の数の誘導デバイス間のカップリングを解析することで、設計サイズを縮小し、ガードリングを削減または排除します。

ロレム・イプサムは、未知のプリンタがタイプのゲラを取り、それをスクランブルしてタイプ標本帳を作った、1500年代以来、業界標準のダミーテキストでした。それは5世紀だけでなく、生き延びてきました

Ansys VeloceRFは、複雑なスパイラル形状のデバイスやTラインの合成とモデリングにかかる時間を大幅に短縮することで、設計サイクルを短縮します。

インダクタのサイズとインダクタ間のクロストークは、ダイのサイズに影響を与える可能性があります。Ansys VeloceRFは、最適化条件とジオメトリ制約を使用して、より小さなデバイスを設計するのに役立ちます。さらに、任意の数のインダクタ間のカップリングを計算して、シリコン実装面積を最適化し、回路のコンテキストでインダクタを最適化します。Ansys VeloceRFでパラメトリックスイープがサポートされることで、回路のコンテキストでの最適なパフォーマンスソリューションとなります。ファウンドリ検証済みの精度により、クロストーク障害を排除するのに役立つシリコン実証済みモデルを使用して設計におけるリスクを軽減します。

Ansys VeloceRFは現在、200を超える独自のファウンドリプロセスをサポートし、TSMC社、UMC社、GlobalFoundries社、TowerJazz社、Samsung社などのすべての半導体ファウンドリのCMOS、BiCMOS、GaAs、SOS、SOIを含む、最小3nmまでのあらゆるプロセスに対応しています。このツールは、主要なEDA設計プラットフォームおよびLVSツールと統合できます。

ロレム・イプサムは、未知のプリンタがタイプのゲラを取り、それをスクランブルしてタイプ標本帳を作った、1500年代以来、業界標準のダミーテキストでした。それは5世紀だけでなく、生き延びてきました

Ansys VeloceRFは、わずか数分で、ミリ波のスパイラル形状デバイスとTラインを合成して解析します。DRC/DFMクリーンデバイスを生成します。これには、最小3nmまでのフィルも含まれます。これらのデバイスは、受動性および因果律を満たすSパラメータおよび非常にコンパクトなRLCkネットリストモデルによってモデル化され、最大限の幾何学的柔軟性をもたらすようPCell/PyCellとして提供されます。コンテキストに応じた最適化により、複数のデバイスや伝送路を密なフロアプランでパッキングすることで、ダイサイズを大幅に削減でき、ガードリングを削減または排除できます。デバイスの構成ブロックが事前定義されたライブラリで高周波をサポートし、任意の数の誘導デバイス間のカップリングをサポートします。

VeloceRFは、シリコン上の誘導デバイスの包括的な合成、モデリング、解析、および最適化を提供します。

Ansysは、障害を持つユーザーを含め、あらゆるユーザーが当社製品にアクセスできることはきわめて重要であると考えています。そのため、US Access Board(508条)、Web Content Accessibility Guidelines(WCAG)、およびVoluntary Product Accessibility Template(VPAT)の最新フォーマットに基づくアクセシビリティ要件に準拠するよう努めています。

エンジニアリング課題に直面している場合は、当社のチームが支援します。豊富な経験と革新へのコミットメントを持つ当社に、ぜひご連絡ください。協力して、エンジニアリングの障害を成長と成功の機会に変えましょう。ぜひ今すぐお問い合わせください。