-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

先端半導体パッケージング技術とは

先端半導体パッケージングとは、複数の半導体チップを組み合わせて1つのパッケージに実装するための一連の製造プロセスです。このアプローチ方法を採用することで、機能が向上し、消費電力とコストを削減できます。

従来のパッケージングは、1区画の土地に平屋の建物を建てるようなものです。先端パッケージングでは、より狭い土地に複数の建物を配置して、橋やシャフト、トンネルでそれらを接続します。こうした技術を効果的に活用する企業は、急速に成長する半導体市場で競争上の優位性を確立できるでしょう。

先端パッケージングで最も多く用いられる手法は、2.5D、3D-IC、異種チップの集積、ファンアウト方式のウェハレベルパッケージング、そしてシステムインパッケージです。どの手法も、ウェハから単一のチップを作成し、プラスチックや金属、またはガラスで囲まれ、電気的に接続された単一のアセンブリ(パッケージ)に、他のチップと一緒に配置するための方法です。作成されたパッケージは、プリント回路基板またはフレキシブルテープに接続され、電子機器に実装されます。

先端半導体パッケージング技術の利点

より狭いスペースにより多くのトランジスタを実装することは、従来の技術では実質的な限界を迎えつつあります。これまで数十年にわたり、マイクロエレクトロニクス業界ではIntel社の共同創業者であるGordon Moore氏が提唱したムーアの法則(チップ内のトランジスタ密度が2年ごとに2倍になるという法則)に基づき、進歩に遅れを取らないように投資と計画を進めてきました。チップの世代ごとにサイズは縮小し、密度が高くなり、デバイスにおける電気接続が性能のボトルネックになっています。先端パッケージングは、

この限界を打破するための有力な手法です。複数のチップを3次元に配置して、チップ間や従来の集積回路内で接続を直接確立することで、ボトルネックを解消し、コストを削減できます。さらに、異なる機能を持つチップを近くに配置することで、消費電力を削減し、速度を向上させ、多機能デバイスを1つのパッケージに実装することで簡素化できるというメリットもあります。

この単一パッケージによるフォームファクターの縮小により、集積工程を、複数の要素で構成されるポスト処理工程から半導体製造工場(「ファブ」とも呼ばれる)の基板工程に移すことで、製造、出荷、在庫にかかるコストも削減します。また、この手法はパッケージングにかかる人件費を大幅に減らすため、人件費が安い地域に設備をわざわざ建設する必要もなくなります。

先端半導体パッケージング技術で製造したモジュールを適用したデバイスの分野

高度な演算能力と、生成されたすべてのデータを格納するための大容量メモリに対する需要が高まる中、効率性に優れた低価格なマイクロエレクトロニクスデバイスに対するニーズが生まれています。また、高性能な消費者向けエレクトロニクス製品に対する需要が高まると、少ない消費電力でより優れた機能を達成する、より小型な製品に対するニーズも高まります。デバイスのスマート化が進み、測定(センサー)、データのインポート、計算(プロセッサ)、データの格納(メモリ)、データのエクスポートなどを実行するコンポーネントが追加されています。先端パッケージングは、製品が備えるべき各機能の複数のインスタンスを1つのモジュールに統合するのに役立ちます。

その実現に向けて最も急速に成長している分野の1つが自動車業界です。性能、効率、安全性を実現する高度なシステムと、センサー数の大幅な増加に伴い、先端パッケージングで製造された、よりロバストで効率的かつ低価格な電子モジュールの需要が高まっています。

複数の電子機能を1つの部品に統合して電子設計に追加するものとしては、IoTデバイスもあります。先端パッケージングを活用したソリューションは、アセンブリの自動化とPCBの複雑さを簡素化しながら、性能を向上させ、コストを削減して電力要求を緩和します。

先端パッケージングは、人工知能(AI)やハイパフォーマンスコンピューティング(HPC)に求められる高いコンピューティング要件を達成するうえでも役立ちます。このアプローチは、より小型で消費電力の少ない構成に対して、より多くの機能を実現します。NVIDIA社をはじめ、AIおよびHPC向けハードウェアのプロバイダ各社は、先端パッケージングのサプライチェーンをすでに確立しています。これらのプロバイダは、電力要求とコストを管理しながら性能を向上させるために必要となる多機能モジュールの製造に、Intel社とTSMC社の先端パッケージング技術を採用し始めています。

先端パッケージングのコンポーネントとテクノロジー

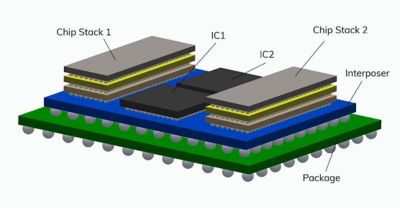

先端半導体パッケージング技術は、複数のテクノロジーを使用してICチップをパッケージに効率的に実装する。

先端パッケージングを理解するために、各コンポーネントと、半導体ファウンドリが使用するさまざまな先端パッケージング技術から説明していきます。

コンポーネント

- チップレット: パッケージレベルで他のチップレット集積や多機能ICチップと組み合わせることを目的として、特定の機能に対して最適化された、パッケージ化されていない個別のダイ。

- ダイ: 1つまたは複数の機能を実行するよう設計された回路が形成された大きなウェハから切り取られた半導体材料のブロック。 ダイを基板または他のダイに接続したものがチップです。

- I/Oパッドやバンプ: チップで信号を送受信するために使用される、チップ表面の導電領域。

- インターコネクト: 2つ以上の回路素子を接続して電流を流すための構造。一般に、1つまたは複数のダイを接続する薄い構造です。

- インターポーザー: 1つまたは複数のチップと基板の間の材料層。先端パッケージングでは、シリコンベースまたはガラスベースの材料を使用します。

- プリント回路基板(PCB): 電子システム内のコンポーネントを電気的に接続する多層回路が形成された平坦な構造。リジッドPCBとフレキシブルPCBがあります。一般的に、リジッドPCBにはFR4、フレキシブルPCBにはポリアミドが用いられます。

- 再配線層(RDL): より効果の高いI/Oパッドを実現する、内部伝導経路を含む1つまたは複数のダイの下に追加される金属層。

- はんだボール: 半導体パッケージ内のコンポーネントを接続するために使用する、はんだ素材の小さなボール。そのサイズは、接続対象によって異なります。

- 基板: パッケージ内で他のコンポーネントを物理的および電気的に接続する回路を含む平らなコンポーネント。IC基板は、半導体材料の層と、FR4またはポリアミドで作られた積層基板で構成されます。

- システムオンチップ(SoC): コンピュータまたは電子システムのすべての機能を1つのチップに統合したICチップ。

- シリコン貫通ビア(TSV): シリコンウェハまたはダイの上面と底面の間の電気接続。これにより、薄い半導体材料がコンポーネント間のインターコネクトになります。

- ワイヤボンディング: ダイと基板の間、または複数のダイの間のワイヤ。従来のパッケージングで主流であった、パッケージ内のコンポーネントを接続するための比較的安価な方法です。

テクノロジー

2.5Dスタックでは、TSVを用いたインターポーザーを使用して、複数のチップをパッケージに接合する。3Dスタックでは、ダイ内に設計されたTSVを用いて、ダイを垂直方向に接合する。

- 2.5D: 2.5Dでは、IC基板に複数のダイを接合する代わりに、ダイと基板の間にインターポーザーを使用します。インターポーザーは、TSVを用いて信号伝搬を実現します。

- 3D-IC: 複数のダイを重ねて配置する方法です。TSVによってダイが接続されます。

- ファンアウト方式のウェハレベルパッケージング: RDLは、チップ上の高密度I/Oパッドから、基板上のより大きなボールグリッドアレイに移行しています。

- システムインパッケージ(SiP): 2.5Dまたは3D-ICを使用して、完全なコンピュータまたは電子デバイスパッケージを製造します。SoCソリューションに必要なすべてのICを配置する代わりに、SiPでは複数のダイを組み合わせて、単一パッケージで同じ動作を実現します。

先端半導体パッケージング技術における課題

スーツケースに荷物を詰める、あるいは最新のGPUモジュールを設計するように、「パッケージング」とは、必要なものをできる限り効率的に空間に収めることです。高度な半導体製造過程では、目標コストを達成しながら、パワーインテグリティ、シグナルインテグリティ、熱的健全性、および機械的応力の問題にも対処する必要があります。

インターコネクト

パッケージ内の各チップを接続し、モジュールを電子デバイスの他の部分に接続するI/Oパッドに接続する必要があります。インターコネクト、TSV、ワイヤなどの伝導経路をパッケージに組み込む必要があります。これらの伝導経路は信号を伝送するため、各経路の信号が隣接経路の信号と干渉しないこと、経路が過度に加熱されないことを確認する必要があります。

電力

電力効率は、市場における大きな差別化要因です。お客様は、より少ない電力でより多くの機能を実現したいと考えるため、パッケージ設計時は、電力の消費と損失を最小限に抑える構成を開発し、先端技術を活用する必要があります。

熱

電流が流れると、パッケージ内のすべてのコンポーネントで熱が発生します。そのため、パッケージには熱の蓄積を最小限まで抑える材料や構成を使用し、コンポーネントから熱を逃して、使用されるデバイスにどのような影響を与えるかを解析できるような熱マネジメントソリューションが必要です。

ロバスト性

パッケージの温度が上昇すると材料は膨張し、下降すると収縮します。そのため、さまざまな材料を使用し、インターコネクトテクノロジーを用いて、各材料の膨張率の違いや材料の膨張と収縮の繰り返しによってインターコネクトやチップで故障が発生しないようにする必要があります。はんだボールの疲労を理解し、自動車、IoT、航空宇宙などの様々な用途における過酷な環境でのパッケージ設計の摩耗や破損といった耐久性を把握する必要があります。

コスト

競争の激しい半導体業界では、コストは重要な検討事項です。配線工程のパッケージングのように、従来のチップパッケージングは人手を必要とし、輸送コストも生じます。先端パッケージングプロセスでは、自動化を活用し、統合テストを含め、基板工程までパッケージングプロセスを前倒しする必要があります。設計者は、コストを考慮しながら選択肢をインテリジェントに検討するために、さまざまな場面で最適化ツールを活用しています。

先端半導体パッケージング技術の未来

半導体サプライチェーンに関わる企業は、より高度なパッケージングを導入し、性能を向上してコストを削減できるようにロードマップを作成しています。Yole Intelligence社が最近実施した調査によると、2022年の業界規模は920億ドルで、先端パッケージングが占める割合は48%でした。同調査では、2028年までに業界規模は1,360億ドルまで成長し、先端パッケージングのシェアは58%まで増加すると予測しています。

次世代のパッケージング製造では、電力効率が高く、比較的低価格のパッケージ、よりコンパクトなチップ設計、システムインチップアプリケーションに対する需要増加に対応するために、新しい材料、より大規模な自動化、革新的なテクノロジーを活用する必要があります。

国や企業の垣根を越えたパッケージングエコシステムにおける競争はますます激化すると予想されています。2023年のCHIPS法の取り組みの1つとして、National Advanced Packaging Manufacturing Program(米国先端パッケージング製造プログラム)に対する30億ドルの資金援助が発表されました。業界を牽引するIntel社、TSMC社、Amkor社は、2023年に新しい先端パッケージング施設を設立するために、それぞれ35億ドル、29億ドル、20億ドルを投資することも発表されました。

エンジニアは、製造工場におけるパッケージング技術のみならず、設計ワークフローに統合できる具体的なパッケージング技術をサポートする優れたソフトウェアツールを探すことになります。たとえば、先日、Ansys、Microsoft社、およびTSMC社は2.5D/3D-ICパッケージングのクラウドベースの応力シミュレーションツールセットを共同で開発しました。

関連リソース

さあ、始めましょう

エンジニアリング課題に直面している場合は、当社のチームが支援します。豊富な経験と革新へのコミットメントを持つ当社に、ぜひご連絡ください。協力して、エンジニアリングの障害を成長と成功の機会に変えましょう。ぜひ今すぐお問い合わせください。