-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

経験豊富な半導体エンジニアまたは設計者として、新しい集積回路(IC)の対称ネットレイアウトを作成したものの、レイアウト後のSPICEシミュレーションで電気的な偽ミスマッチが見つかったことを想像してみてください。この直感に反する結果により、設計に戻って非対称性をチェックすることになりますが、何も見つかりません。一体何が起こっているのでしょうか?

この電気的な偽ミスマッチ効果は、寄生抵抗回路網のノード上における寄生結合容量の分布の差によって引き起こされることが判明しています。これは、寄生抽出と寄生抽出ソフトウェアのアーティファクトが原因です。

ここでは、このような偽ミスマッチ条件を識別し、レイアウトの差による実際のミスマッチと区別するための実践的な推奨事項を説明します。寄生抽出ソフトウェアであるAnsys ParagonXは、こうしたアーティファクトを回避し、ポストレイアウトシミュレーションとIC設計フローの信頼性を確保するのに役立ちます。

IC設計におけるデバイスとネットのマッチング

多くのアナログおよび高周波(RF)ICは、デバイスとネットのマッチングの概念に依存しています1,2。このような回路の例としては、StrongARMラッチ、センス増幅器、差動ペア、電流ミラー、多相クロックなどがあります。ネットとデバイスをマッチングさせることで、ある程度の余裕が生まれ、回路が避けられないプロセスのばらつきに対応できるようになります。

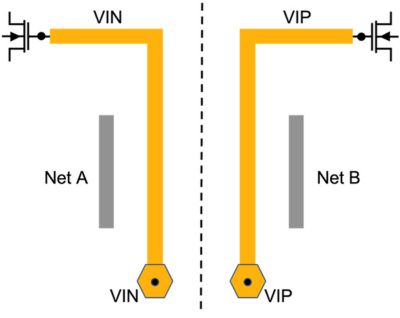

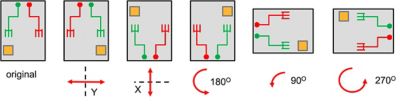

設計者が完全なネットマッチングを実現するためには、X軸またはY軸を中心に設計を反転させたり、セルを移動または回転させたりして、対称レイアウトを作成します(図1参照)。

しかし、設計ルール、配線可能性、形状の制約により、完全な対称性やマッチングを実現することは困難です。そのため、標準的なポストレイアウト設計フローの一環として、寄生抽出を行ってマッチングを検証してから、ポストレイアウト回路をシミュレーションします。シミュレーションによって期待通りの良好な結果が得られたのなら、最高の対称性とマッチングが達成されたことになります。測定した信号にオフセット、ミスマッチ、差異がある場合は、マッチングが不十分であるため、レイアウトを改善する必要があります。

真の難題

真の難題は、ネットが完全に対称でマッチングしていても、ポストレイアウトシミュレーションで電気的挙動に差が出ることがよくあることです。典型的なシナリオでは、2つのネットが容量と抵抗で良好なマッチングを示すものの、RC遅延(ギリシャ語の小文字のτで表される)で大きなミスマッチがある場合があります。常識と物理学の基本的な知識から考えると、容量と抵抗がマッチングしていれば、遅延もマッチングするはずであり、このシナリオにおいては、遅延のミスマッチは直感に反します。

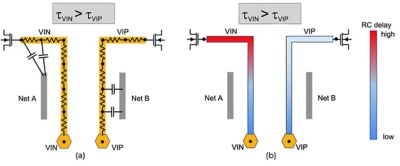

図1.マッチングされたネットVINとネットVIPのレイアウト。入力ポートはVINとVIPで、目的地点はMOSFETのゲート。寄生抵抗、結合容量、およびRC遅延のマッチングを確実にするためには、ネットとその環境を対称に作成する。

図2.(a)寄生素子(抵抗と容量)を可視化したもの。ネットVINとネットVIPの結合容量の分布に差(非対称性)があることに注意。(b)ネットレイアウト全体にわたるRC遅延を可視化したもの。結合容量がネットVINの遠端(ポートVIN側)とネットVIPの近端に集中しているため、VINの遅延がVIPの遅延よりも大きくなっている。

問題が寄生抽出ソフトウェアにあることも判明しています。具体的に言うと、遅延のミスマッチの根本原因は、寄生抽出ソフトウェアが抵抗回路網のノードに結合容量をどのように分布させているかに関連していますが、何らかの理由で結合容量の分布が大きく非対称になっています(図2参照)。

このような非対称性の最も可能性の高い理由は、抽出ソフトウェアで使用される計算ジオメトリアルゴリズムの異方性です。こうしたアルゴリズム(スイープまたはスキャンラインやポリゴン境界の横断など)では、左右、上下、時計回り・反時計回りなどの特定の方向を優先し、レイアウトを3Dシステムではなく平坦なシステムとして扱います。これにより、システムは、理論的には優先方向を変換できるはずの本来の重層構造とセルの変換特性を失うことになります。

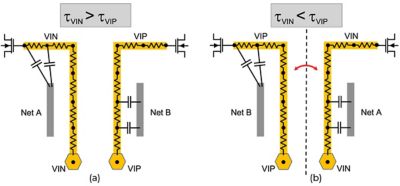

この仮説を検証するために、いくつかのGDSファイルを対象にして、ポストレイアウトネットリストの解析とポストレイアウトシミュレーションを行い、一連の実験を実施しました。元のDSPFファイルは、基準として使用し、X軸とY軸に対する対称反射や、90度、180度、270度の回転など、さまざまな変換によって得られたDSPFファイルと比較しました。図3は、対称変換の結果を示したものです。

図3.(a)元のGDSファイルと(b)反転したGDSファイルのRC寄生。ケース(a)とケース(b)では、ネットVINとネットVIPの結合容量の分布が逆になっている。左側と右側のネットにおける結合容量の分布は、ケース(a)とケース(b)の両方で同じである。

予想通り、左側のネットにおける結合容量の分布は、元のレイアウトでも反転したレイアウトでも同じでした。これは、右側のネットでも同じことが言えます。しかし、ネットVINとネットVIPが元のレイアウトから、反転したレイアウトに変わったため、ケース(a)のネットVINの結合容量の分布が、ケース(b)のネットVIPの結合容量の分布となりました(その逆も同様)。

この容量分布の変化は、VINとVIPのRC遅延のシミュレーション結果とよく一致しました。RC遅延τは、ケース(a)ではネットVINの方がネットVIPよりも大きいものの、ケース(b)ではネットVIPの方が大きくなっています。同様に、ポストレイアウト回路シミュレーションでも差が見られ、ネットVINの遷移時間がケース(a)ではネットVIPよりも大幅に大きくなりましたが、ケース(b)では小さくなりました。このことから、前述のように、対称なネットVINとネットVIP間の電気的ミスマッチが寄生抽出ソフトウェアのアーティファクトであることが分かります。

もちろん、レイアウトを変換しても、ネットVINとネットVIPの結合容量やRC遅延の差の符号が変わらないのであれば、その差はレイアウトのミスマッチによるものであるため、レイアウトを修正する必要があります。

寄生抵抗回路網上の結合容量の分布

この実験は、対称レイアウトにおける結合容量の異方性および非対称分布に関連する寄生抽出のアーティファクトを調査した最初の事例かもしれません。

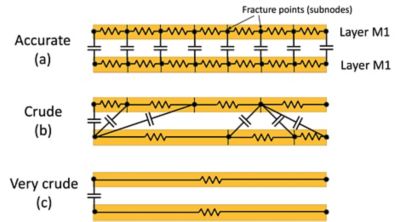

偽ミスマッチ効果は、さまざまな設計、技術、ファウンドリ、および3つの主要な寄生抽出ソフトウェアで観察されました。偽異方性の程度は、抽出ソフトウェアによって異なります。これは、3つの寄生抽出ソフトウェアで、正確なものから、粗いもの、非常に粗いものまで、結合容量分布の品質がそれぞれ異なるからです(図4参照)。

どの寄生抽出ソフトウェアも、ポストレイアウトシミュレーション(SPICE、EMIR、タイミングなどのツールを使用)にかかる時間を短縮するために、寄生RC回路網のサイズを最小限に抑えようとします。ネットリストのサイズ(シミュレーション時間)と精度の間には常にトレードオフが存在します。これを行うのは、物理的な認識レベルや精度が異なるさまざまな寄生抽出ソフトウェアなのです。

図4.寄生抵抗回路網のノード上における結合容量の分布。最も正確なのがケース(a)であり、ケース(b)は正確さに欠け、ケース(c)は非常に粗い。

シミュレーションと解析結果

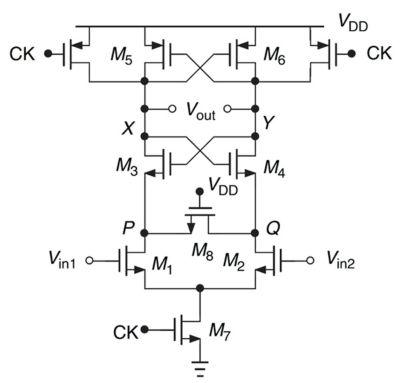

5nm FinFET技術で実装されたStrongARMラッチ3(図5参照)のポストレイアウトSPICEシミュレーションにより、デバイスM1とデバイスM2の遷移時間のミスマッチが約500fsであり、このミスマッチの上限スペック(約30fs)を大幅に上回ることが明らかになりました。レイアウトは比較的小さく、目視検査では非対称性が見られませんでした。設計者とレイアウトエンジニアは、シミュレーションでのミスマッチを解消するために、レイアウトの修正を何度も繰り返しました。しかし、2週間以上かけたものの、解決には至りませんでした。

そこで、Y軸を中心にレイアウトを反転させたところ、ポストレイアウトネットリストにおいて、-370fsという符号が反転したミスマッチが確認されました。この結果は、+500/-370fsのミスマッチが寄生抽出ソフトウェアのアーティファクトに起因するものであることを示す明確で説得力のある証拠です。

電子設計自動化(EDA)ツールのParagonXを用いてネットのミスマッチを解析した結果、ネットin1とネットin2の間に15%を超える大きなRC遅延差があることが確認できました。この差の符号は、元のレイアウトと反転したレイアウトで変わります。その後、ParagonXを使用して結合容量を可視化したところ、その分布に強い非対称性があることが確認されました(これらのプロットは、第三者の機密保持のため、このブログで紹介することはできません)。

興味深いことに、ネットin1とネットin2の抵抗とネット間結合容量の両方が非常に高い精度で一致しました。抵抗は0.05%未満の精度で一致し、結合容量は0.2%未満の精度で一致しました。これは、多くのポストレイアウトネットリストで見られる一般的な現象ですが、マッチングされたネット上の容量と抵抗の値が非常に近いものの、このブログで説明した効果によってRC遅延がかなり異なる場合があります。

0.2%の容量差は、ルールベース(パターンマッチングベース)の容量抽出の不正確さが原因であると考えられます。ユーザーが精度目標を設定し、それに基づいてランダムウォークベースのフィールドソルバー(FS)を使用することで、容量抽出の精度を大幅に向上させることができます。回路動作において容量マッチング(またはSAR ADCのコンデンサアレイに対するバイナリ/非バイナリ重み付け)が重要になるネットに関しては、ネットFS抽出モードを選択して使用することが常に推奨されています。

結果について

図5.StrongARMラッチの回路図。ネットin1とネットin2のRC遅延は一致させる必要がある。

ポストレイアウト回路シミュレーションは、カスタムトランジスタレベルのIC設計を解析およびシミュレーションするための標準的手法と考えられています。観測された偽ミスマッチ効果は、ポストレイアウトシミュレーションの精度はどの程度なのか?という興味深い疑問を引き起こします。言うまでもなく、ポストレイアウトシミュレーションの精度は、寄生抽出ソフトウェアの精度を上回ることはできません。また、容量と抵抗の抽出は一般的にかなり正確ですが、寄生抵抗回路網のノード上に結合容量を粗く分布させると、過渡およびACシミュレーションで約500fs(またはそれ以上)の誤差が生じる可能性があります。この調査結果は、精密かつ迅速なアナログ設計、タイミング解析、およびその他の用途におけるSPICEシミュレーションの信頼性と精度に重要な影響を与える可能性があります。少なくとも、業界はこの問題を検出、デバッグ、解決、または回避するための方法を確立する必要があります。

同様に重要なのは、抽出のアーティファクトによって引き起こされた偽ミスマッチが、マッチングされたネットのレイアウトやコンテキストの違いによって生じる実際のレイアウトおよび電気的ミスマッチを覆い隠してしまう可能性があるということです。偽ミスマッチが存在する場合には、本当のミスマッチを検出することが困難、あるいは不可能になることがあります。また、偽ミスマッチと本当のミスマッチが偶然に相殺されると、本当のミスマッチがゼロまたは小さなミスマッチのように見えることがありますが、これもまた高いリスク要因となります。

実践的な推奨事項

以下の推奨事項を考慮してください。

- 回路設計者およびレイアウトエンジニアへの推奨事項:

a. 一般的なミスマッチと、特に寄生抽出の誤りによって引き起こされる偽ミスマッチにもっと注意を払うこと。

b. これらの効果についての認識を高めること。EDAツールベンダーに対し、結合容量の分布に関連する寄生抽出の精度を向上させ、このようなアーティファクトを取り除くよう要請すること。

c. マッチングされたネットの容量抽出を正確に制御するために、FSを使用すること(容量のマッチングが重要な場合)。

d. ParagonXなどのEDAツールを使用して、ポストレイアウトネットリストにおけるネットとデバイスのマッチングを積極的にチェックおよび検証し、こうした問題をデバッグするとともに、レイアウトのマッチングを改善すること。

- EDAツールベンダーへの推奨事項:寄生抽出ソフトウェアの精度を向上させ、特に結合容量の分布品質を高めること。

- ファウンドリへの推奨事項:ネットのマッチングと結合容量の分布品質に対応する寄生抽出ソフトウェアの検証と適格性確認をより徹底して行うこと。

- EDA研究者への推奨事項:ポストレイアウトネットリストのサイズを急激に大きくすることなく、その精度を向上させるより優れたアルゴリズムと手法を考案すること。

- すべての関係者への推奨事項:寄生抽出によって生じる可能性のある偽ミスマッチが設計フローに紛れ込んでいないか確認すること。

a. 元のレイアウトに対称変換を適用してレイアウトを作成する(図6参照)。たとえば、以下のような方法がある。

i. X軸を中心に反転させる。

ii.Y軸を中心に反転させる。

iii. 180度回転させるか、90度または270度回転させる(DRCが許可する場合)。

b. 寄生抽出を行う。

c. ParagonXを使用して、元のレイアウトと変換後のレイアウトのポストレイアウトネットリストを比較する。

i. ParagonXは、SPICEよりもはるかに迅速かつ簡単にミスマッチを検出し、デバッグすることができる。

d. ParagonXが使用できない場合は、ポストレイアウトのSPICEシミュレーションまたは別の解析ツール(STAなど)を用いて、2つのポストレイアウトネットリストを比較する。

e. 偽ミスマッチを示唆する有意差がある場合:

i. レイアウトの目視検査を行う(可能な場合)。

ii. 寄生抽出ソフトウェアベンダーとファウンドリに調査結果を報告する。

図6.ネットの偽ミスマッチを特定するのに役立つレイアウト変換。電気特性は、これらの変換に対して不変であるため、寄生容量、抵抗、遅延、デバイス、SPICEシミュレーションも不変でなければならない。

ICレイアウト寄生解析およびデバッグソフトウェアであるAnsys ParagonXが、IC設計における電気的な偽ミスマッチの問題をどのように解決するかをご確認ください。

参考文献

[1] “The art of analog layout,” 2nd ed., A. Hastings, Prentice Hall, 2005.

[2] “CMOS IC Layout: Concepts, Methodologies, and Tools,” D.Clein, Newnes, 1999.

[3] “The StrongARM Latch” (A Circuit for all seasons), B.Razavi, IEEE Solid-State Circuits Magazine, v. 7, no.2, p. 12-17, 2015.

お客様におすすめのリソースをご用意しています。

詳細はこちら

ICレイアウト寄生解析およびデバッグソフトウェアであるAnsys ParagonXが、IC設計における電気的な偽ミスマッチの問題をどのように解決するかをご確認ください。

Advantageブログ

Ansys Advantageブログでは、専門家が投稿した記事を公開しています。Ansysのシミュレーションが未来のテクノロジーにつながるイノベーションをどのように推進しているかについて最新の情報をご覧ください。