-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

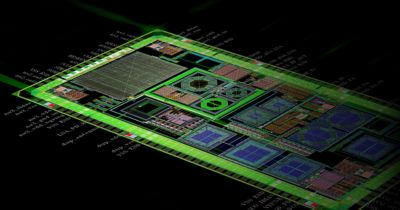

半導体設計における寄生成分とは、相互接続配線によって生じる意図しない電気的影響や相互作用を指します。寄生成分は複雑な形で回路の挙動を変化させるものであり、その影響は以前は軽視されていたものの、現在では重要な因子と見なされています。アナログインターコネクト寄生成分の解析とデバッグは、複数のベンダーや個別のツールの寄せ集めに依存することが多く、複雑化するマルチフィジックス要件に対して明確な戦略がないのが実情です。

アナログIC(チップ)は、半導体の黎明期から使用されており、アナログ設計のエンジニアは、より大規模で華やかなデジタルチップの設計手法やエコシステムとはまったく異なる手法を用いてきました。しかし、ワイヤレス接続、電気自動車、データセンターでの高速デジタル接続、マルチダイ3D-ICの普及といった強力な市場動向を背景に、ここ数年でアナログ設計に対する需要が大幅に増加しています。その結果、大手の設計企業は、競争力を維持しながら、この市場機会を活かすために、より効率的で優れたアナログ設計フローの構築に注力するようになりました。

アナログ設計のトレンドと課題

デジタルICの世界とは異なり、アナログ設計では、大規模で高密度なデジタル設計に最適な最先端のシリコンプロセス技術を積極的に追い求めてはいません。実際、アナログ設計者は、通常は小型で高速な回路で信号品質をより制御できる、成熟した旧世代のプロセスを好む傾向がありますが、需要の急増に伴い、さまざまな課題が浮き彫りになりました。

- 名目上、シリアライザ/デシリアライザー(SerDes)のようなデジタル通信チャネルであっても、信号速度は増加し続けており、より正確で包括的な電磁界解析が必要になっています。

- システムオンチップ(SoC)のアナログ部分に関しては、主にデジタルチップの他の部分と同じ高度なシリコンプロセスを使用しなければならないため、こうした高度なノードでの設計を複雑にするシリコン効果に対処する必要があります。

- お客様がより優れたソリューションを求める中で、アナログ設計の規模が拡大しており、特にメモリ、フェーズドアレイレーダー、3D-ICインターポーザー、イメージセンサーなどの回路に対応する従来のアナログ設計ツールの処理能力に大きな負荷がかかっています。

こうした技術的な課題はすべて、最大の課題である、設計者の生産性に関する問題に直結しています。アナログチップの納期と設計コストは、そのチップの開発プロセスの所要時間によって決まります。アナログ設計のエンジニアは、多くの時間を回路解析とデバッグに費やしており、これらの作業によって、プロジェクト期間全体の35~50%、場合によってはそれ以上の時間が費やされていることが分かっています。予測不可能なことが多いデバッグは、非常に時間がかかることがあります。これは、設計の挙動を理解するために、複数回のシミュレーションを実行し、さまざまな抽出および解析ツールを使用する必要があるからです。特に高度なシリコンプロセスでは、レイアウト寄生成分が重要な因子となり、場合によっては能動素子(トランジスタ)の挙動に大きな影響を及ぼすことがあります。インターコネクトの効果と寄生成分は、回路の挙動と総設計コストの両方を左右する重要な要素となっています。

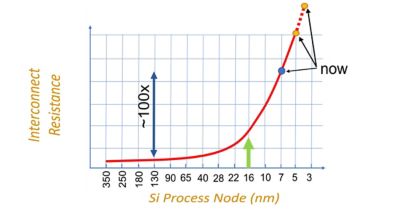

寄生成分の影響が増大している理由としては、寄生抵抗および容量(RC)値の増大と、寄生要素の増加が挙げられます。これにより、シミュレーション時間が長くなるとともに、複雑な非線形相互作用が直感に反する形で現れ、設計者が理解して修正するのが困難になることがよくあります。

シリコンプロセスノードが微細化するにつれて、寄生抵抗が急激に増加する。これは、現代のアナログ設計において寄生抵抗が重要な因子となる要因の1つである。

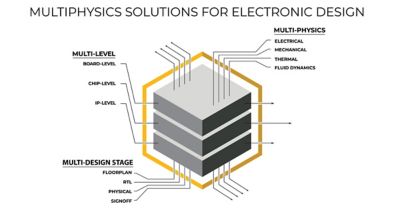

もちろん、アナログ設計チームが成果を上げるには、レイアウトインターコネクトによって引き起こされる多くのマルチフィジックス現象に対処できるように、十分に考え抜いた戦略を持たなければなりません。戦略は、今日の問題だけでなく、今後さらに複雑になるであろう要件にも対応する必要があり、これには、炭化ケイ素(SiC)などの新しい材料や、フォトニクスなどの新しい物理分野が関わる可能性があります。

多くの企業は、設計フローの穴を埋めるために、ポイントソリューションを段階的に導入してきました。その結果、現在では、さまざまなベンダーと連携してインターコネクト解析を行う断片的なアプローチをとっています。私たちは、今こそ一歩立ち止まり、インターコネクトマルチフィジックス領域を独立した専門分野として捉え、レイアウトプラットフォームやシミュレーションソフトウェアを選択する際に使用されるのと同じ戦略的アプローチでこの領域に取り組む時だと考えています。

インターコネクトマルチフィジックス領域に対応する戦略的ソリューション

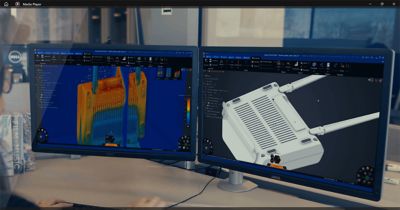

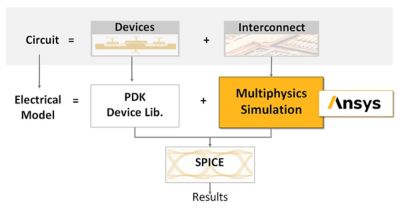

測定ができないものは、修正もできないと言われています。プロセス設計キット(PDK)に含まれる能動素子用の電気モデルは、専用のライブラリ特性評価ツールスイートで作成された後、容易に再利用できるようにライブラリに保存されます。しかし、これはインターコネクト寄生成分には当てはまらず、下図に示すように、各レイアウトを設計案ごとに一から抽出しなければならないため、アナログ設計エンジニアはインターコネクト解析に多くの時間と労力を費やしています。Ansysは、インターコネクト解析を独立した設計課題として重視しており、設計チームに統合的で戦略的なソリューションを提供しています。

Ansysは、高速設計、高度なプロセスノード、極めて大規模なアナログ回路における寄生相互作用の解析およびデバッグで直面する生産性と精度の課題に対応する包括的で戦略的なソリューションを提供している。

Ansysは、寄生相互作用の根本原因解析を通じて、設計に関する幅広い知見を設計者に提供することを目的とし、半導体に対するインターコネクトの効果をすべてカバーする信頼性の高いファウンドリ認証済みの多様なマルチフィジックスソリューションを提供しています。この統合マルチフィジックスアプローチは、優れた解析結果を導き出す高精度が実証されたエンジンと、時間を節約する高効率のデバッグ機能を提供します。マルチスケールソリューションにおける長年の優れた実績を持つAnsysが提供するこれらの半導体向けマルチフィジックスツールは、パッケージ、PCB、3D-IC、さらには製品レベルまで対応します。

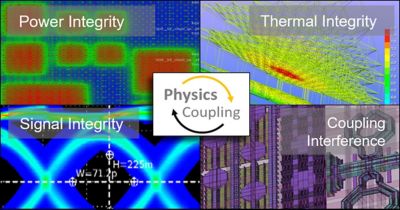

Ansysのインターコネクトマルチフィジックスソリューションには、アナログ設計やミックスドシグナル設計にとって重要な以下のすべての分野に対応する製品およびプラットフォームが含まれています。

- RC寄生成分:高度かつ大容量の抵抗および容量寄生解析により、根本原因を数分で特定できるため、特に最上位階層の解析においてデバッグ時間を大幅に短縮することができます。

- 高周波電磁界:高周波(RF)、ミリ波、5G、Wi-Fi、SerDes、物理層インターコネクト(PHY)、アナログ-デジタルコンバータ(ADC/DAC)などの高速設計には、配線間のすべての連成場のモデリングが不可欠です。高速インターコネクトの特殊な用途として、インダクタや伝送経路があり、これらには、特定の設計および解析機能が必要です。

- 熱:長年にわたって実証されてきた統合型熱エンジンでは、AI駆動のメッシュ生成と業界をリードする電圧降下解析を組み合わせて、局所的なジュール自己加熱、過渡熱、システムレベルの冷却、周囲熱など、半導体デバイスの層ごとの温度マップを特定することができます。

- 熱-機械:機械的応力と反りは、温度勾配と材料の不一致が原因です。これらの機械的問題により、製品の信頼性が損なわれるだけでなく、応力による電気的変化が生じる可能性があります。

- 電圧降下およびエレクトロマイグレーション(EM/IR):ファウンドリがサインオフ要件としてみなしている電圧降下解析ツールでは、電源線とアナログ信号線の両方の静的および動的電力損失を特定することができます。また、製品の長期的な信頼性を確保するには、エレクトロマイグレーション解析が不可欠です。

- パワーデバイス解析(RDS-ON):高出力デバイスの電力損失や過熱を回避するためには、設計段階で高出力デバイス内およびスイッチ内の寄生要素を極めて高い精度でモデル化する必要があります。

- フォトニクス:より高速なデータレートを実現するCo-Packaged Optics(CPO)が注目を集めるようになり、多くの設計チームが、熱安定化や機械的応力の大幅な低減など、光エレクトロニクスに関連する新たな物理的課題に取り組むようになりました。

- シグナルインテグリティ:高帯域メモリ(HBM)インターフェースなどの3D-IC上にインターポーザーインターコネクトとダイ間の信号パスを実現するには、通信チャネル全体を正確にモデル化するための専用のシグナルインテグリティ解析機能が必要です。

- 静電放電(ESD):どのチップにも、電気的過大応力による損傷を防ぐ保護回路として機能するアナログ素子が搭載されています。設計の規模が大きくなり、業界がマルチダイ設計を採用する中、最終的なサインオフ段階で行われている従来の解析がボトルネックとなっています。新しい手法を利用すれば、設計フローの初期段階でESD解析をはるかに迅速に行うことができます。

- 基板ノイズ:高感度のアナログ設計には、特にシリコン基板へのノイズ注入が重要であり、ノイズ源とその分布の物理特性の包括的なモデリングが必要です。

- アンテナ設計:効率的な無線およびレーダービームフォーミングを実現するには、自由空間での伝播だけでなく、アンテナ周辺にある物体との相互作用も高精度にモデル化する必要があります。

回路の挙動に大きな影響を及ぼす寄生インターコネクト効果は、さまざまな物理的要因が複雑に絡み合ったものになっています。これらの課題に断片的に対処しようとすると、効率が低下して、設計コストが増加し、設計の最適化が円滑に進みません。インターコネクト解析市場には、他の重要な設計分野と同様の戦略的な考え方でアプローチする必要があります。そうすることで、現在の効率を向上させるだけでなく、技術需要の加速に伴う将来の新たな要件にも対応できるように設計フローを最適化することもできます。

Advantageブログ

Ansys Advantageブログでは、専門家が投稿した記事を公開しています。Ansysのシミュレーションが未来のテクノロジーにつながるイノベーションをどのように推進しているかについて最新の情報をご覧ください。