クイックスペック

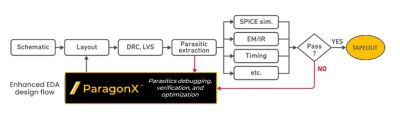

ParagonXは、設計がLVSクリーンでない状態でも、早期のレイアウト段階で寄生成分に関連した設計上の問題を特定できる、プロセスに依存しないツールです。レイアウト寄生成分の影響を理解することは、特に高度なプロセスノードで製造された設計において重要です。これにより、設計プロセスの後半で性能のボトルネックや弱点による生産の遅れを回避できます。大規模なネットリストを処理できる優れたスピードと容量により、ICレイアウトのエンジニアは寄生成分の問題の根本原因を特定して修正できるため、設計品質の向上と設計サイクルの短縮につながります。