-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

動的電圧降下解析は複雑な解析プロセスです。適切な解析を正しく行うには、多数の入力ファイルとさまざまな構成設定の組み合わせが必要です。

動的電圧降下解析では、スイッチングシナリオが鍵となります。設計内のすべてのゲートとインスタンスが同時にアクティブになるわけではありません。また、より複雑なセルでは、スイッチングの可能なモードが多数存在します。これらのインスタンスが切り替わる正確な時間がそれぞれ異なる場合もあります。同じ場所の近くで、多くのインスタンスが同時または短時間のうちに連続して切り替わると、局所的な電圧降下が多発する可能性があります。スイッチングシナリオとは、時間の経過とともに各インスタンスで発生するスイッチングに関するデータを指します。動的解析の価値は、スイッチングシナリオの質に左右されます。スイッチングシナリオによって、より短いシミュレーション時間でより多くの電圧降下違反を発見できれば、グリッドのロバスト性をより容易に向上させることができます。

このスイッチングシナリオを作成する方法には、さまざまものがあります。まず考えられる方法は、他の場所で行った機能シミュレーションによって生成されたデータを使用することです。このデータは、ベクトルファイルで利用できます。利用可能なファイルフォーマットにはVCD(Value Change Dump)とFSDB(Fast Signal Database)があり、最も一般的なのはFSDBですが、ここでは、「VCD」という用語を用いて、両方のベクトルファイルを指すこととします。VCDを使用することは、動的解析に必要なスイッチングシナリオ情報を取り込むシンプルで分かりやすい方法です。

ただし、VCDを入力として使用する電圧降下解析には多くの制約があります。まず、VCDの入手が課題です。なぜなら、本格的な機能シミュレーションは設計サイクルの終盤になって初めて行われるからです。電圧降下解析を開始するのに、そんなに長くは待てません。さらに、VCDは一部の機能モードに対してのみ利用可能であり、電圧降下解析に最適とは限りません。

長時間のVCDにわたる電力プロファイリング

パワーインテグリティ解析を行うエンジニアの大半は、解析ソフトウェアによって効率化できるベクタレス手法を使用してスイッチングシナリオを作成することを好みます。これらのベクタレス手法には、設定の柔軟性が高く、スイッチングカバレッジが広いという利点がありますが、ベクタレススイッチングシナリオが実際の機能モードではないという欠点があります。

この段階で使われるのがレジスタ転送レベル(RTL)VCDです。このVCDはフロントエンド設計の検証段階で利用できます。ゲートレベルまたはネットリストレベルのVCDに比べて、RTL VCDは設計サイクルの非常に早い段階で利用可能で、機能モードよりもはるかに長期間存在し、入手も容易です。

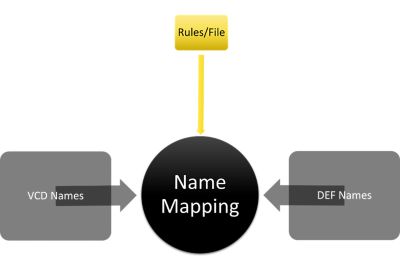

RTL VCDをパワーインテグリティ解析に取り入れる場合には、主に2つの課題に直面しますが、これらはソフトウェア自体で軽減できます。1つ目の課題は、設計のRTL段階で生成されるVCDの名前が合成中に変更されてしまうことです。そのため、RTL VCD内の信号と、ネットリストまたは設計交換フォーマット(DEF)のピンやネット間で適切な名前マッピングを行う必要があります。これは、適切な名前マッピングを行い、文字列パターンや合成中の一般的な名前変更を調査して、それをパワーインテグリティソフトウェアにコード化することで対処されます。ユーザーは、合成やフォーマル検証の段階からデータを取得し、名前マッピングファイルとして取り込むこともできます。

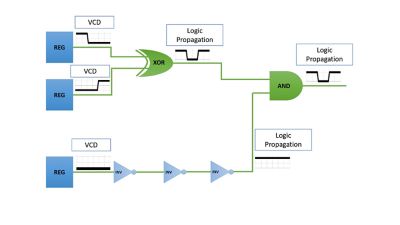

2つ目の課題は、設計内の順次要素のためにのみ存在するイベントやスイッチングモードを設計全体(組み合わせ論理やクロックツリーネットワークなど)に伝播させる必要があることです。この課題も、電圧降下解析ソフトウェアが解決します。このソフトウェアは、セルの機能を推測し、フリップフロップから組み合わせ論理へイベントを伝播させることができます。イベントの正確な時間は、遅延伝播から導き出したり、各インスタンスの到着時間を含む静的タイミング解析(STA)ファイルを入力として使用して求めたりすることができます。

VCDの名前マッピング

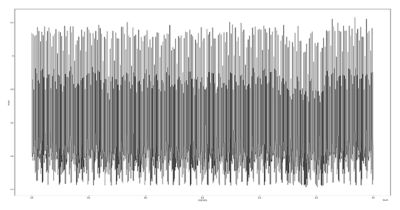

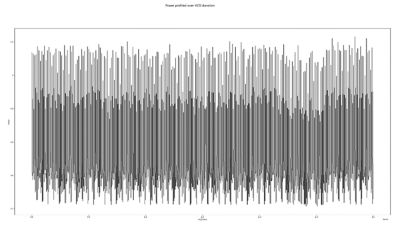

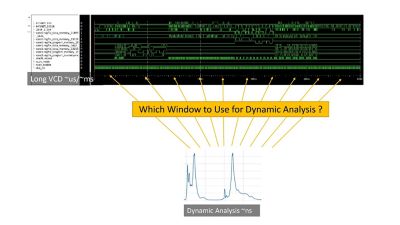

次の課題は、RTL VCDに限ったものではありません。VCDを入力として使用し、動的電圧降下解析を行う場合には、VCDの期間内から小さな時間枠を選択する必要があります。VCDがゲートレベルであれRTLであれ、その期間が長く、数マイクロ秒から数ミリ秒にも及ぶことがあります。複数のVCDが存在する場合もありますが、過渡的なパワーインテグリティ解析は、ナノ秒レベルのより短い期間で実行することが望ましいため、VCD時間枠を選択しなければなりません。

ユーザーは通常、何らかの形式のVCDプロファイリングを使用します。最も一般的な方法は、消費電力が最も高いVCD時間枠を選ぶことです。消費電力が高ければ、電流も大きくなる傾向があり、大電流によって、ほとんどの電圧降下違反の問題が見つかると考えられます。このプロファイリングの段階では、VCDの期間全体を通して小さな間隔ごとに消費電力を測定します。その後、このデータを用いて、消費電力が最も高い時間枠を特定します。他にも、電力の変化が最も大きいVCD時間枠を探す方法や、領域ごとに電力値を調べる方法、これらを組み合わせて使用する方法などの高度な方法があります。また、ユーザーは抵抗とタイミングウィンドウの重なりに関するデータを活用し、VCD時間枠選択プロセスをより最適化することもできます。時間とリソースの利用状況に応じて、複数のVCD時間枠で電圧降下解析を行うことも可能です。

VCD電力のプロファイリング

デジタルおよび3D集積回路(3D-IC)用のAnsys RedHawk-SCパワーインテグリティサインオフプラットフォームを含むAnsysの半導体チップ設計ソリューションは、10年以上にわたり世界中の多くのトップ企業によって利用されています。RedHawk-SCは、RTLとゲート間で名前をマッピングし、さまざまなお客様と何世代もの技術にわたる無数の設計に貢献しています。このプラットフォームは、より効率的にマッピングできるようにインテリジェンスや設定/ノブを追加することで改良を続けており、その結果、非常にロバストな名前マッピングメカニズムを備えるようになりました。

同様に、RedHawk-SCは、取り扱う高度な設計の範囲が広く、克服すべき課題の質も高いため、特にイベントの伝播に効果的です。また、設計のクロックネットワークに正確な論理イベントが反映されることを保証するフローも備えています。ほとんどの統合クロックゲート(ICG)は、合成後に設計に挿入されるため、RTL VCDには記録されません。RedHawk-SCは、VCDイベントから信号を順次インスタンスごとに伝播させることで、これらのICGのイネーブルピンで発生する論理信号を推測することができます。その結果は後にこれらのICGをゲートする際に利用されます。これにより、ICGとその下流のクロックネットワークには、RTL VCD入力に対応するイベントが反映されることになります。

RedHawk-SCは、電子設計自動化を支援するクラウド最適化ビッグデータ解析プラットフォームであるAnsys SeaScapを基盤としています。これにより、ビッグデータ解析が半導体設計解析の分野に役立つようになります。Seascapeプラットフォームは、分散コンピューティング処理を可能にするだけでなく、データを処理して実用的な結果を得るための新しい方法を定義することもできます。これはVCD時間枠選択の未来であり、より多くのデータを電力プロファイリングの情報と組み合わせることで、さらに最適な解析フローを実現できるようになります。

RTL VCDは、動的電圧降下解析に適したスイッチングシナリオを選択するという複雑な課題を解決する効果的なソリューションです。このフローを有効にする際の課題には、VCDの名前マッピング、イベントの伝播、ベクトルの時間枠選択などがあります。また、RedHawk-SCは、ロバストなVCD名前マッピングフローと、論理イベントの伝播を行うためのネイティブソリューションに加え、他のデータポイントからの入力で簡単に拡張できる効率的な電力プロファイリングフローも備えています。

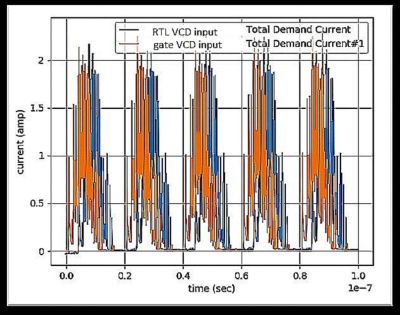

RTL VCDと、同等のゲートVCDを入力として使用した際の電流需要と論理イベント伝播を比較したもの

VCD信号による、レジスタから設計全体への論理イベントの伝播

AnsysのRedHawk-SCとその他の半導体設計ソリューションの詳細をご確認ください。

Advantageブログ

Ansys Advantageブログでは、専門家が投稿した記事を公開しています。Ansysのシミュレーションが未来のテクノロジーにつながるイノベーションをどのように推進しているかについて最新の情報をご覧ください。