-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

ASIC設計フロー: ASIC設計とは

ASICとは

ASICは、Application-Specific Integrated Circuit(特定用途向け集積回路)の略で、電子システム内で特定の機能または機能セットを実行するよう綿密に設計された特殊な集積回路です。電子レンジやテレビなど、よく目にする電気製品に搭載された汎用マイクロプロセッサとは異なり、ASICは特定用途に合わせてカスタマイズされ、極めて高い効率と性能を発揮します。

ASICは、さまざまなエレクトロニクス製品に採用され、外部の電子回路要件を最小限まで抑えます。特定用途に合わせてカスタマイズされるという性質上、ASICの開発には、より高いコストがかかります。ただし、この高いコストは大量生産品を設計する場合には正当化され、費用対効果が高いと見なされることもあります。

ASIC設計のタイプ

ASICの設計には、主に次の2つの方法があります。

- ゲートアレイ(セミカスタム設計)

- フルカスタム設計

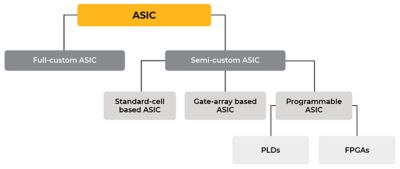

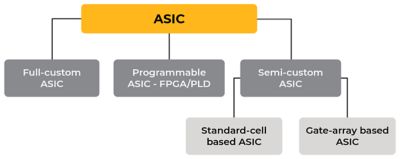

セミカスタム設計は、いくつかのグループに分けられます。ASICの分類を以下に示します。

ASICのタイプ

プログラマブルASICは、セミカスタムASICとは別のものと見なされることもあります。他のASICの分類を以下に示します。

ASICの分類

フルカスタム設計: フルカスタム手法はより複雑でコストがかかりますが、ゲートアレイ手法よりもはるかに多くのことが可能です。設計に必要なゲートや電子部品のみが組み込まれ、未使用のゲートが削除されるため、ASICのサイズが大幅に減少します。これらのASICは特定の目的に合わせて設計され、最終製品の特定の機能をサポートします。

セミカスタムASIC: この手法では、拡散層、トランジスタ、およびその他の能動素子を事前に定義して、初期設計作業を最小限に抑えることで、開発コストを削減します。 メタライゼーションプロセスを使用するため、生産サイクルは大幅に短縮されます。フルカスタム設計よりも迅速なプロセスです。最終設計段階で特定のスイッチを開閉して操作し、目的の仕様に従ってチップの挙動を変化させます。

スタンダードセルベースASIC: このタイプのASICでは、ゲート、マルチプレクサ、フリップフロップなど、スタンダードセルと呼ばれる事前に設計されたロジックセルを使用します。スタンダードセルは、フルカスタム設計手法を使用して作成され、ASIC設計の基本的な構成ブロックとして機能し、同じ性能と柔軟性を達成しながら、時間とリスクを削減します。

ゲートアレイベースASIC: このASICカテゴリでは、トランジスタ、ロジックゲート、およびその他の能動素子がシリコンウェハ上に作成されて製造されますが、製造中にインターコネクトが形成されません。事前に設定されたゲートアレイ上のトランジスタの配置は「ベースアレイ」と呼ばれ、ゲートアレイを形成する最小反復要素は「ベースセル」と呼ばれます。この手法は、所要時間の短縮、ロジック密度の向上、接触層のカスタマイズなど、いくつかの利点があります。

プログラマブルASIC: このタイプのASICは、製造後にハードウェアレベルでプログラミングできます。特定用途向けにカスタム設計および製造された従来のASICとは異なり再プログラミング可能なため、高い柔軟性をもたらします。プログラマブルASICの例としては、プログラマブルロジックデバイス(PLD)やフィールドプログラマブルゲートアレイ(FPGA)があります。

ASICの適用分野

ASICは、さまざまな業界で採用されており、各分野独自の目的のためにテクノロジーが活用されています。ここでは、ASICが重要な役割を果たす主な分野をいくつか紹介します。

消費者向けエレクトロニクス製品: ASICは、スマートフォン、デジタルカメラ、スマートテレビなど、あらゆる消費者向けエレクトロニクス製品に搭載されています。個々にカスタマイズされたソリューションを提供できるため、デバイスの全体的な性能と電力効率を向上させています。

電気通信: ASICは、ネットワーク機器、ルータ、通信デバイスで採用されています。カスタム設計が可能であるため、最適な機能性とデータ処理速度が保証されます。

自動車: ASICは、自動車業界で幅広く採用されており、エンジン制御装置(ECU)、先進運転支援システム(ADAS)、インフォテインメントシステムなどのさまざまなシステムに組み込まれています。

ヘルスケア: 医療機器、診断機器、イメージングシステムの多くには、精度、信頼性、および電力効率に関する厳しい要件を満たすためにASICが組み込まれています。

ASICの設計プロセス

ASICの設計は、いくつかの段階を伴う綿密なプロセスであり、それぞれが高度に特化したチップの作成に寄与します。ASICの設計の主な段階には、次のものがあります。

仕様と要件: 設計プロセスを開始するための仕様と要件を定義するASIC設計フローの最初の段階です。関連するステークホルダーからの意見を収集し、全体にわたる製品仕様を詳細な技術仕様に変換する段階です。期待される出力、性能目標、消費電力目標、その他の重要なパラメータを明確に設定する必要があります。

アーキテクチャ設計: 仕様を定義した後、ASICのアーキテクチャを設計します。具体的には、全体的な構造、機能ブロックの配置、そしてこれらのブロック間の相互接続を決定します。エンジニアは、考えられる多くのアイデアを引き出し、性能への影響、技術的な実現可能性、ハードウェアリソースを慎重に検討しながら、割り当てられた予算内に総コストが収まるように、理想的なアプローチを選択する必要があります。

RTL設計: レジスタ転送レベル(RTL)設計では、ハードウェア記述言語(HDL)を用いてASICの機能を記述します。この段階は、抽象的なアーキテクチャ設計と物理的な実装の間の橋渡しとなります。

検証: 検証では、テストベンチで設計をテストおよびシミュレーションすることで、ASICが指定された要件を満たしていることを確認します。この段階は、設計上の欠陥や問題を特定して修正する上で不可欠です。

合成と実装: 合成時に、RTLコードはASICの物理的実装を表すゲートレベルのネットリストに変換されます。このネットリストはレイアウトに変換され、物理的な設計は消費電力、速度、面積の観点から最適化されます。

サインオフとテープアウト: 物理的なレイアウトが完了すると、次のステップではファウンドリが推奨する設計ルールに照らして物理的な設計を検証します。エンジニアは、LVS(layout-versus-schematic)チェックと設計ルールチェックを実行します。ここでは、シミュレーションツールを使用して、必要に応じて設計を変更します。このプロセスはサインオフと呼ばれます。指定された設計ルールに対して設計が合格と判定されると、テープアウトされ、製造のためにファウンドリに送られます。

製造: 最後のステップは、半導体製造プロセスを使用したASICの製造です。このステップでは、カスタム設計されたチップを製造できる半導体ファウンドリとのコラボレーションが必要です。最適なファウンドリを選択することで、目的の結果を得ることができます。

ASICの利点

性能の最適化: ASICは、特定のタスクで優れた性能を発揮するように設計されており、専用機能に不可欠な回路のみを備えています。その効率化された設計は、サイズと消費電力の削減という点で汎用プロセッサを上回る極めて高い性能と効率を達成します。

電力効率: カスタム設計されるASICの性質上、不要なコンポーネントは排除され、電力効率が向上し、エネルギー消費量が削減されます。

スペースの最適化: ASICは、具体的なフォームファクターに合わせてカスタマイズできるため、電子機器のスペース効率の高い設計が可能です。

大量生産での費用対効果の向上: ASICの設計および製造の初期コストは高くなりますが、冗長なコンポーネントがないため、大量生産することで費用対効果が高くなります。

性能と効率の向上は、エレクトロニクス業界で常に最優先課題として挙げられています。ASICの用途に特化した性質が業界全体に与える影響は明らかであり、イノベーションを推進し、電子機器の機能を向上させます。ASICの設計プロセスをより効率的で迅速、かつ費用対効果の高いものにするには、設計およびシミュレーションソフトウェアを慎重に選択する必要があります。スピードの向上とサイズの縮小により、設計者は新たに生じるマルチフィジックスの課題に対応できるように従来の手法から移行する必要があります。

マルチフィジックスシミュレーションの重要性については、こちらをご覧ください。Ansysの半導体ソリューション

関連リソース

さあ、始めましょう

エンジニアリング課題に直面している場合は、当社のチームが支援します。豊富な経験と革新へのコミットメントを持つ当社に、ぜひご連絡ください。協力して、エンジニアリングの障害を成長と成功の機会に変えましょう。ぜひ今すぐお問い合わせください。