-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

Ansysブログ

June 29, 2023

無線周波数集積回路(RFIC: Radio Frequency Integrated Circuit)とは

携帯電話や無線インターネットアクセスからレーダーやナビゲーションシステムまで、世界は無線周波数(RF)通信を使用して接続されるようになっています。この技術の進歩により、無線周波数集積回路(RFIC)はそれ自体が複雑なチップとなり、非常に大規模なシステムオンチップ(SoC)ソリューションに集積されています。RFICは通常、数百MHzから数GHzの範囲の高周波で動作するように設計されています。

無線回路設計の目的は、高コストを発生させることなく、許容可能な品質により、送信元と宛先の間で信号を送受信することです。これは、実証済みの設計方法を使用して回路を設計することで実現できます。RFICは通常、アンプ、フィルタ、ミキサー、発振子、変調器/復調器から構成され、1つのチップに集積されています。

RF回路設計は、低周波アナログ設計技法とマイクロ波回路の設計に使用される手法の両方を利用する離散技術です。マイクロ波設計と低周波アナログ設計の主な違いは、伝送線路原理の重要性にあります。マイクロ波設計は伝送線路の概念に大きく依存しますが、低周波アナログ設計はそうではありません。その結果、インピーダンスレベルの選択、信号サイズ、ノイズ、歪みの描写に影響があります。

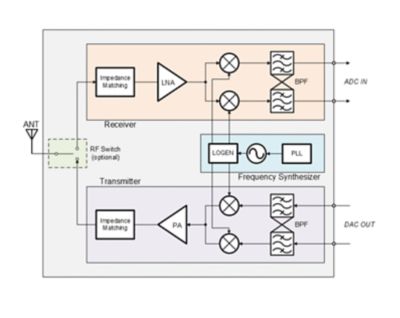

一般的な無線周波数(RF)集積回路のブロック図

RFIC設計の主なコンポーネントは次のとおりです。

アンテナ: 無線周波数信号を送受信するために使用されます。

フィルタ: 特定の周波数帯域の信号を制限します。特定の周波数範囲を通過させる帯域フィルタ(BPF)、特定のレベルより低い周波数を通過させる低域フィルタ(LPF)、特定のレベルより高い周波数を通過させる高域フィルタ(HPF)などがあります。

インピーダンスマッチング: ソースと荷重のインピーダンスをマッチングして、信号反射を最小限に抑えたり、電力伝送を最大化したりします。

低ノイズアンプ(LNA): 受信した信号がミキサーを直接通過するほど強くないため、弱い信号を増幅し、ノイズ応答をフィルタリングします。

変調器: 信号の変調に使用します。通信チャネルの要件を満たすために、特定の方法で信号をエンコードします。トランスミッタの「アップコンバーター」として機能し、低周波アナログ信号とローカル発振子信号を組み合わせてRF信号を生成します。

復調器: 受信側の信号をデコードします。変調された搬送波から元の情報伝送信号を抽出します。

パワーアンプ: ミキサーの出力をより高い出力に増幅して送信するために使用されます。カバレッジの範囲は、伝送の効率に応じて増加します。

RFスイッチ: 高周波信号を伝送パスを介してルーティングします。

RFICの使用例と利点

- 無線通信と接続: RFICは、携帯電話、IoTデバイス、家電などの無線通信に広く使用されています。RFIC対応デバイスは、日常生活に不可欠なものとなっています。コンパクトな統合、電源管理、高速データ転送は、その最大の利点の一部です。

- 車載レーダーシステム: RFICは、衝突回避、アダプティブクルーズコントロール、パーキングアシスタンスなどの用途の車載レーダーシステムで使用されています。コンパクトなフォームファクターにより、車両に簡単に取り付けることができるため、安全性が向上します。

- 無線センサーネットワーク: RFICは、環境監視、スマート農業、産業オートメーションなどの用途の無線センサーネットワークで利用されています。センサーノード間の無線接続により、広範なケーブル配線とインフラストラクチャが不要になります。RFICベースのアプリケーションを使用すると、RFICベースのネットワークを簡単に拡張または再構成できるため、柔軟性とスケーラビリティが得られます。

- 衛星通信: RFICは、信号増幅、周波数変換、変調などの衛星通信システムで使用されます。広いカバレッジ、高いデータ転送速度、効率的な信号処理など、多くの利点があります。

最新のRFICの設計と検証

数十年にわたり、アナログ/ミックスドシグナル設計(AMS: Analog/Mixed-Signal)設計は技能と見なされており、RFICの設計者は回路図とレイアウトの段階を経て物理的な検証と回路シミュレーションに至る独自の手動による技法を持っていました。しかし、これはプロジェクトの時間と予算の両方でコストがかかります。

これらの従来の設計および検証方法は、最新のRFIC設計標準を満たすには非効率的です。設計者がアナログ、デジタル、およびRFを大規模なSoCに統合しようとすると、動作周波数が増加し続けるため、事前に定義されたデバイスライブラリやその他のレガシー手法を使用してRF集積回路を設計することは困難です。さらに、高周波での電磁相互作用は、信号反射、クロストーク、電磁干渉(EMI)などの寄生効果をもたらし、回路パフォーマンスを低下させるため、設計サイクルのできるだけ早い段階で考慮する必要があります。

最新のRFIC開発フローでは、可能な限り最高の回路パフォーマンスを達成しながら、各設計反復の所要時間(TAT)を短縮する必要があります。したがって、設計とシミュレーションは反復プロセスで密接に関係しています。シミュレーションの出力に従って、設計が複数回微調整されます。これは長いプロセスであり、設計者は非常に積極的なプロジェクトスケジュールに従って提供するために回路のパフォーマンスを妥協することがあります。妥協のないパフォーマンスを実現するために、RFIC設計者は、高度な電子設計自動化(EDA)ツールと、IC設計に特化した優れたシミュレーション機能を必要としています。

EDAツール、特に回路図ツールとレイアウトツールをシリコン最適化シミュレーションソフトウェアとシームレスに統合することは、RFIC設計を成功させるための鍵となります。このツールのハイパーコンバージェンスにより、回路図の初期段階から成熟したレイアウト段階までの回路の高速かつ正確なモデリングが可能になります。また、動的電圧降下、エレクトロマイグレーション、その他の問題の組込みチェック機能も備えています。AnsysはSynopsys社と協力して、現在のRFIC設計者のニーズを満たし、信頼性と堅牢性を保証する統合ソリューションを提供しました。

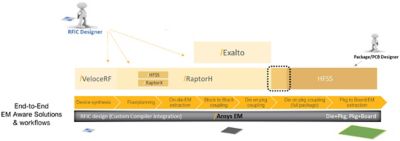

Ansysのシリコンで最適化された電磁場シミュレーションワークフローは、設計サイクルの初期段階から開始されます。Ansys VeloceRFを使用すると、高速で正確なデバイス合成とモデリングを実現できます。フロアプランニング段階で情報に基づいた意思決定を行うために、RFIC設計者はオンチップ設計とワークフロー専用の電磁ソルバーであるAnsys RaptorXを使用します。RaptorXは、レイアウトのすべての受動素子と配線をモデル化し、複数のブロック、またはダイとパッケージ間の結合を共同解析できます。RFIC設計者は、Ansys RaptorHインターフェースを介してICデータベースをAnsys HFSSに渡し、システムレベルのシミュレーションを行うことができます。このインターフェースでは、フルダイ、パッケージ、およびPCB電磁場シミュレーションを実行できます。サインオフ段階では、Ansys Exaltoは、電磁的に重要なRF回路のすべての部分について電磁モデルを使用して、明確なRC結果を向上させます。電磁モデルはRCテストベンチで自動的にバックアノテートされ、電磁的な信頼性を備えた高速なレイアウト後シミュレーションが可能になります。

RFICおよび高速SoC向けAnsys電磁場解析対応ワークフロー

AnsysによるRFIC設計のための包括的なソリューションは、信頼性が高く堅牢なソリューション、歩留まりの向上、所要時間の短縮を実現します。

VeloceRF、RaptorX、RaptorH、およびExaltoは、業界をリードする電磁界ソリューションであり、設計者が設計サイクル時間を数桁短縮し、RFICのパフォーマンスを大幅に向上させるのに役立ちます。

より複雑で洗練されたRFICを必要とする5Gのような高速かつ信頼性の高い無線接続に対する需要により、新しいRF技術の開発が推進されています。これらの課題に対処するために、設計者は高度な設計手法、包括的なシミュレーションツール、最適化されたアルゴリズムを使用して、設計プロセスを合理化し、市場投入までの時間を短縮できます。

RFICの設計と検証を共同で開発することにより、設計者は高品質で信頼性の高いICを提供することができます。設計者は、VeloceRF、RaptorX、RaptorH、およびExaltoソリューションを活用して、EDA設計ツールとの統合を容易にし、精度を向上させ、市場投入までの時間を短縮することができます。

RF回路のためのAnsys電磁場解析手法の基礎については、ウェビナー「Foundations of Silicon-optimized Electromagnetic Methodology for RFICs」をご覧ください。