-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

Ansysブログ

February 29, 2024

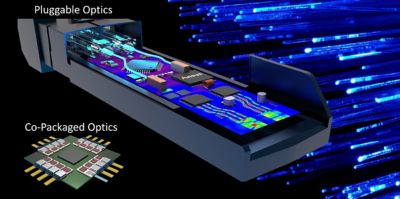

Co-packaged Opticsとは

Co-Packaged Optics(CPO)は、今日のデータ量の多いネットワークにおいて、帯域幅密度、通信レイテンシ、銅線での到達距離、電力効率などの複雑さが増す問題に対処するためのアプローチです。これは、通信に必要な重要な要素、すなわち光学とエレクトロニクスを緊密に連携させることで実現します。

現在、業界では光入出力(OIO)やCPOなどの異なる用語が使用されており、特にNear-Package Optics(NPO)がCPOと誤ってラベル付けされることが多いため、混乱が生じています。明確にすると、CPOのより広いトレンドはOIOと同じであり、3次元集積回路(3D-IC)パッケージに光学デバイスが集積されたチップレットベースのテクノロジーへの移行が進んでいます。

プラガブル光トランシーバとその将来像

高解像度ビデオストリーミング、バーチャルリアリティ、モノのインターネット(IoT)、ハイパフォーマンスコンピューティング(HPC)、人工知能と機械学習(AI/ML)によって取り扱うデータ量が急速に増え続けており、ネットワークやデータセンターは、帯域幅の拡大、レイテンシの削減、電力消費の削減に対する需要の高まりにグローバル規模で直面しています。

当初は長距離通信でのみ主流であった光学デバイスは、短距離通信においてもデータセンターで広く普及されるようになり、プラガブル光トランシーバによってラックとの間およびラック内の帯域幅密度が向上しています。これらのトランシーバは、100Gから400G、800G、そして1.6Tまで進化してきましたが、特にAIのようなデータ集約型アプリケーションでは、高速通信において消費電力が大きな問題となります。さらに、帯域幅の拡張性とプラガブルデバイスのフォームファクターは、6.4Tや12.8Tなどの将来の容量で限界をもたらす可能性があります。

こうした問題に対応するために、業界はCPOやOIOに積極的に投資しており、新たに出現したアプリケーションによって進化するニーズと将来の大容量ネットワーク要件に対応するようにカスタマイズされた次世代ソリューションの先駆けとなるよう準備しています。さまざまなコンソーシアム、マルチサプライヤー契約、Institute of Electrical and Electronics Engineers(IEEE)やOptical Internetworking Forum(OIF)などの標準化機関の間でのコラボレーションにより、CPOソリューションの仕様の調整が行われています。

プラガブル光学デバイスとCo-Packaged Opticsの比較

Co-Packaged Opticsの長所を享受

Broadcom社およびCisco Systems社の初期のCPOソリューションでは、消費電力で30~50%の削減、インターコネクト消費電力でおよそ1pJ/bit未満を達成すると示されています。また、Ayar Labs社は、5pJ/bit未満での双方向スループットとして16Tbpsを実現しました。一般に、CPOはいくつかの方法で消費電力の節約を達成します。

- 損失が生じる銅配線ゼロ: プラガブル光学デバイスとは異なり、CPO設計では、特定用途向け集積回路(ASIC)チップから、エネルギーを吸収する銅線リンクを介して基板上そして前面パネルまで信号を通過させる必要がありません。代わりに、CPO設計はファイバーをスイッチに直接配置することで、チップと光学エンジンの間で短距離での低損失通信を実現します。

- デジタルシグナルプロセッサ(DSP)の削減: レーンあたり25Gを超える速度を実現する現在のアーキテクチャでは、信号の劣化、歪み、タイミングの問題を積極的に解析して補正するために、DSPベースのリタイマーがプラガブル光学デバイスに必要なコンポーネントとなっています。DSPは、システム全体の消費電力を最大25~30%増加させることに寄与しています。しかし、CPOにより、ASICと光学デバイスの間のオフチップの損失を生じさせる銅配線が排除されることで、設計者は1つのDSPレベルを安全に排除して、電力を節約し、コストを削減できます。

- 集積レーザー: レーザー光源の配置については、2つの考え方があります。一般的なアプローチでは、外部レーザーが使用されます。これは、ファイバーを介した光の伝送とCPOへの結合を必要とし、通常は30~50%の光パワー損失を生じさせます。別のアプローチでは、レーザーをチップ上に直接集積し、熱マネジメントとレーザーの信頼性が実現できることを条件に、前のアプローチと比較して大幅に高い光結合をもたらします。

- 高帯域幅と低レイテンシ: CPOは、DSPの数が少なく、長い銅配線を排除することで、より高い帯域幅と低いレイテンシを実現できます。DSPのような追加のブロックや銅配線の寄生成分はすべて、CPOソリューションでは見られない信号遅延をもたらします。

Co-Packaged Opticsの適用

ネットワーキング用のCPO: CPOの主なアプリケーションは、データセンター内のサーバーを接続するためのフロントエンドネットワークです。前述の高帯域幅、低レイテンシ、電力効率などの利点により、CPOはネットワーキングアプリケーション向けの次世代光イーサネットテクノロジーを実装するための有望なアプローチです。

OIO(AI/ML用のHPC): 光学業界は、AI/MLの作業負荷に対応するために、OIOによって実現されるAIバックエンドネットワークと呼ばれる新しいファブリックを検討しています。

コンピューティングにおいては、従来のサイロ化されたHPCアーキテクチャでの柔軟性のないリソース割り当ての課題は、長年のデータ転送速度の制限に収束し、帯域幅容量の顕著なボトルネックと多様な作業負荷の処理における非効率性を生み出します。中央処理装置(CPU)やグラフィックス処理装置(GPU)の処理速度が急激に上昇するにつれて、既存のI/Oインフラストラクチャはそれに追いつくことが困難になっており、処理装置が頻繁にデータを待つような非効率性につながっています。

AI/MLの作業負荷の要求が高まるにつれて、この問題はさらに重要になります。そのためには、高速、低レイテンシ、ロスレスデータ転送、拡張性を特徴とするネットワークファブリックが必要になります。ここに、現状に革命をもたらす可能性があるOIOの重要性があります。

HPCにおける分散アーキテクチャの進化においては、メモリ、コンピューティング、ストレージを最先端のOIOによって相互接続されたクラスタに分離することで、サイロ化された制約を克服しようとしています。この戦略的な転換により、動的なリソース割り当てが可能になり、データセンターの多様な作業負荷に対応する際の従来のアーキテクチャの非効率性を解決できます。

CPOの主なアプリケーションは、データセンター内のサーバーを接続するためのフロントエンドネットワークです。

Co-Packaged Opticsの問題の理解

- ベンダーロックイン: スイッチと光学デバイスが単一のベンダーから供給される状況は、ハイパースケーラーの柔軟性と自由度が潜在的に欠如していることを意味します。特定ベンダーのエコシステムに多額の投資を行うと、他のベンダーの製品に移行するのが困難になる可能性があります。そうなると、コンポーネントの切り替えやアップグレードを容易に行うことができなくなり、依存関係や制約につながります。

- 信頼性と現場での可用性: プラガブルは、高度にモジュール化されており、障害時に迅速に交換したり、任意のベンダーからスワップイン/スワップアウトしたりできます。CPOでは、光学デバイスの交換にはスイッチ全体の引き抜きが必要となるため、複雑なサービスタスクを実行するための高度な専門知識が必要です。この問題を解決するために、一部のCPO設計では、レーザーなどのリスクが高いアクティブコンポーネントを、現場交換が容易でプラガブルなリモートモジュール上に分散しています。また、プラガブルな光コネクタを検討しているケースもあります。

- 熱マネジメント: 電気パッケージ内にフォトニック集積回路(PIC)を配置すると、熱クロストークが生じる可能性が高まります。フォトニックダイ内のヒーターやレーザー源からの熱出力は、パッケージの温度マップに影響を与え、電気ダイ内で生じる熱とシステム全体の冷却メカニズムは、PICの熱挙動に影響を与えます。そのため、ダイレベルからシステムレベルまでの完全な熱解析が必要です。

- シグナルインテグリティとパワーインテグリティ: シグナルインテグリティとパワーインテグリティを保証するには、システム全体の過渡シミュレーションが必要です。これには、パッケージ段階で導入されたさまざまなタイプの電気相互接続から生じる追加の寄生効果を考慮しながら、自己矛盾のない電気回路およびフォトニック回路のシミュレーションが必要になります。

- 拡張性とビーチフロント: CPOとOIOの重要な指標はビーチフロント(チップのエッジに沿った帯域幅密度)です。通常、ファイバーはエッジカップリングされます。特定の基板サイズに対するファイバー数を制限する最小ファイバー間隔要件があります。導波路とファイバーの寸法に大きな差がある場合、エッジカップリングソリューションではファンアウトが固有の問題となります。基板サイズを増大させることなく、数千のファイバーを収容する必要があると想像してみてください。V溝を使用すると、ファンアウトなしのエッジカップリングソリューションのためにファイバーを垂直方向に向けることができます。マイクロレンズを使用したグレーティングベースの結合も、他の革新的なソリューションとあわせて検討されています。

- ファイバーアタッチメント: ファイバーアレイからパッケージへの光信号の効率的な結合は、困難な作業です。ファイバーのアラインメント(パッシブアラインメントまたはアクティブアラインメント手法により達成)、傾斜、構造管理および熱マネジメント、製造性、可用性など、いくつかの考慮事項があります。設計者は、光結合設計を慎重にモデル化し、最適化する必要があります。

- 製造性とテストしやすさ: 設計を商業的に実行可能にするのは、低いコストと高い歩留まりです。特にマルチベンダーのサプライチェーンでは、一貫した品質と効果的なテスト手順が需要と投資とともに発展し続ける不可欠なハードルとなります。

電気パッケージ内にフォトニック集積回路(PIC)を配置すると、熱クロストークが生じる可能性が高まります。

関連する市場トレンドの調査

チップレットの登場: チップレットは、基本的に単一のチップとして動作するように同じパッケージに組み込むことができる小さな個々のダイです。業界ではシステムオンチップから単一パッケージのチップのシステムに移行しています。チップレットは、CPOの導入に関与したり、導入を加速させたりする可能性があります。このチップレットアプローチは、1つのパッケージでさまざまなテクノロジーと機能を混在させることを可能にします。たとえば、OIOチップレットは古いCMOSノードをベースにしているのに対し、ASICはより高度なノードを使用しているため、コストを抑え、ダイの歩留まりを向上させることができます。

3D-ICによる集積密度: 半導体業界では、3D-ICテクノロジーにより集積密度が向上しています。今日のCPOアプローチの多くには、低損失基板上に光学チップと電気チップを隣り合わせに配置することが含まれますが、3D-ICの進歩により、超低消費電力および超高帯域チップ間通信を使用してOIOとASICを3Dに集積するマルチダイチップレットCPOが可能になります。この集積密度により、設計が大きく複雑になるため、新たに出現する物理効果を解析するためのマルチフィジックスおよび電磁界(EM)シミュレーションの必要性が高まっています。

Linear-drive Pluggable Optics(LPO): 既存のプラガブルテクノロジーも、なくなったわけではありません。CPOと同様に、LPOはプラガブル光学デバイスからDSPを排除することで省電力を実現します。CPOで光学デバイスとエレクトロニクスが近接して配置されることで、従来のプラガブルモジュールよりも数桁の小型化が実現しました。しかし、この小型化は、プラガブルデバイス自体にも採用され、大きなフォームファクターを改善することができます。

市場の期待に応え、CPOの実行可能性に対するエンドユーザーの信頼を得るには、ロバストなマルチベンダービジネスモデルと大幅なコスト削減、さらには電力削減を実証する必要があります。CPOやOIOの採用を加速するために業界のトレンドとテクノロジーを活用するには、光学コミュニティがIPブロックや光学インターフェースの規格など、欠落している重要な部分を導入する必要があります。設計およびシミュレーションソフトウェアのプロバイダから、デバイスおよびチップの設計者、システムアーキテクチャからパッケージングハウス、テスト機器のプロバイダ、ファウンドリまでのサプライチェーンに携わるすべての人のコラボレーションが必要です。エコシステムを育てることは、確かに時間がかかる大きな取り組みです。しかし、AI/MLのような極めて大規模なアプリケーションの登場により、競争は始まっています。

Co-Packaged Opticsの詳細およびモデリングについては、Ansys Optics製品カテゴリーページと、フォトニック集積回路用の集積マイクロレンズおよびグレーティングカプラのモデリングなど、さまざまな例を集めたアプリケーションギャラリーをご覧ください。