-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

-

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

Ansysブログ

May 16, 2023

低消費電力ICの設計: 手法とベストプラクティス

低消費電力IC(集積回路)の設計は、デバイスのエネルギー消費量を削減してバッテリ寿命を延長する上で、最新エレクトロニクスにおける極めて重要な要素です。バッテリ駆動デバイスの市場が拡大していることで、チップ設計者はICの消費電力を削減するために、さまざまな手法を慎重に検討する必要があります。ICの静的消費電力と動的消費電力を削減するための手法はいくつかあります。DC電流とリーク電流は静的電力源ですが、動的電力はトランジスタスイッチングや短絡電力から生じ、周波数に依存します。

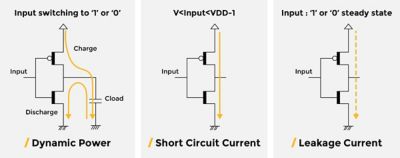

図1: 相補型金属酸化膜半導体(CMOS)回路の電力成分

低消費電力ICの設計には、全体的な消費電力に寄与する消費電力の個々の成分を削減する必要があります。図1には、動的電力特性と静的電力特性が示されています。相補型金属酸化膜半導体(CMOS: Complementary Metal Oxide Semiconductor)インバータの動的帯電により、消費電力はクロック周波数に正比例します。アクティビティのないときに生じるトランジスタからの電力漏れが静的電力となります。

低消費電力ICの設計者は、電源電圧を制御し、回路の複雑さを軽減してクロック周波数を低減し、DC電流源とスイッチングノードの静電容量を監視することで、総消費電力を削減できます。あらゆるものが接続されているため、低消費電力設計手法をテストして使用し、設計の性能を最適化することで、これらの要因間のトレードオフを図る必要があります。

低消費電力設計の手法とベストプラクティス

クロックゲーティング

デバイスの消費電力を削減する1つの方法は、レジスタ転送レベル(RTL)で設計を微調整することです。これは、動的消費電力を削減するための最も一般的な手法の1つです。RTLレベルでは、トランジスタの論理状態が変化しているとき、または負荷静電容量の帯電のために電力が使用されているときに、電力が消費されます。総動的電力は次のとおりです。

Pdynamic = Pcap + Ptransient = (CL + C) Vdd 2 f N3

ここで、CLは負荷静電容量、Cはチップの内部静電容量、fは動作周波数、Nはスイッチングされるビット数です。不要なときにクロックをゲーティングすることで、動的な電流の流れを簡単に削減できます。追加の消費電力を回避するには、AND/NORゲートを使用する代わりに、ラッチベースのクロックゲーティングを使用します。ICの特定の部分へのクロック信号をオフにすると、それらの領域のトランジスタのスイッチングが発生せず、電力が消費されないため、消費電力を大幅に削減できます。

電源遮断

ICでは、すべてのブロックが常に動作するわけではありません。デバイスでの使用方法によって異なります。特定のインスタンスでブロックが機能しない場合には、そのブロックに電力を供給する必要はありません。機能しないブロックへの電源をオフにすることで、消費電力を削減できます。この手法を効率的に使用するために、絶縁ブロックを使用して、電力が遮断されたブロックから不要な信号が送信されるのを防止できます。

周波数ゲーティング

チップには複数のブロックが含まれていますが、各ブロックの動作には最大周波数は必要ありません。周波数要件に基づいてブロックを分離して、異なるブロックに異なるクロック信号を与えることが最良の手法となります。これにより、ICの局所的な動的消費電力を大幅に削減できます。

多段電圧設計

設計内の各ブロックの動作は、必ずしも同じ電力量を必要としません。ブロックの性能とその電圧要件に応じて、チップをパーティション分割できます。電圧要件が高いほど、消費電力量は高くなります。異なる電圧入力を持つ電源アイランドを作成することで、IC全体の消費電力を容易に削減できます。

動的電圧および周波数スケーリング

電源アイランド手法には制限があります。ブロックへの電圧供給をいったん設計すると、後で変更することはできません。動的電圧スケーリング手法は、要件に応じて後で電圧を変更できる柔軟性をもたらします。設計者は、変動する電流に応じて、各ブロックに供給される電力を変更するレギュレーターをプログラミングできます。同様に、電圧スケーリングと周波数スケーリングを組み合わせることで、ソフトウェアプログラムを使用して、各ブロックに供給されるクロック信号を変更できます。

電力低減

最も重要な電力低減手法は、チップの電源電圧を下げることです。FinFET設計では、動的スイッチング電力が支配的であり、電源電圧の2乗に比例するため、超低電圧(ULV)プロセスに対する注目が大幅に高まっています。

漏れ電力のトレードオフ

漏れ電力は、Pre-FinFETテクノロジーにおける重要な消費電力であり、多段電圧ライブラリでの制御が最適です。これらのライブラリは、各セルに対して、それぞれが異なる性能/漏れのトレードオフを図る2つまたは3つのバージョンを提供します。これにより、タイミングクリティカルパスでは高速で漏れがあるセルを使用し、それほどクリティカルでないパスでは低速で漏れの少ないセルを使用できます。

全体として、ICの消費電力を削減するために使用できる多数の手法があります。これらの手法を実装し、適切な設計およびシミュレーションツールを使用することで、設計者はこれらの課題を克服できます。エンジニアは、Ansys RedHawk-SCなどのツールを使用することで、あらゆる設計段階で設計の振る舞いをシミュレーションして予測できるため、エネルギー効率が高く、バッテリ寿命が長い低消費電力ICを設計できるようになります。

低消費電力設計における課題

- 特に超低電圧設計では、電圧降下のマージンが非常に狭くなります。この進化により、最新のIC設計において電圧降下(IRドロップ)サインオフの検証は不可欠となりました。

- 電源電圧が低いと、パスタイミングが動的電圧降下(DVD)の影響を大幅に受けやすくなります。また、実行されるすべてのスイッチングシナリオを捕捉するのに十分なカバレッジでDVDを解析することは非常に困難です。DVDのタイミングへの影響を最小限に抑え、予期しないIRドロップの影響による周波数損失を回避するには、慎重な電圧降下解析が不可欠となります。

- 多段電圧領域では、異なる電圧領域間での適切な信号遷移とシグナルインテグリティを確保するために、慎重な管理が必要です。UPFは、この課題に対処するために設計された規格です。

- 電源遮断を行うと、ブロックを再度オンにしたときに、電気的そして論理的にも困難な遷移現象を引き起こします。

- クロックゲーティングは、クロック分配ネットワークのルートにできる限り近い位置で実装した場合に最も効果的ですが、イネーブル信号のタイミングの実行可能性(時間通りに到着できるかどうか)によって制限されます。これにより、達成された電力効率と設計最適化にかける労力のバランスをとるトレードオフが生じます。

電力解析の妥当性は、回路アクティビティに大きく依存します。しかし、現実的かつ代表的なアクティビティシナリオを作成して、あらゆるモードで実際の使用方法で発生する可能性があるすべての電力レジームを捕捉することは簡単ではありません。よくある間違いは、機能検証アクティビティベクトルを使用して電力を計算することです。これらの計算を行っても正しい判断をできず、電力解析には無関係です。適切なアクティビティベクトルは、手動で作成、電力ツールで自動的に作成(ベクタレス)、または実際のアプリケーションを実行するハードウェアエミュレータで作成できます。

Redhawk-SCは、IC設計の電力解析に広く使用されているソフトウェアツールです。チップの電圧降下を正確に予測および解析するための包括的な機能セットを提供することで、この問題に対処します。RedHawk-SCは、高度なアルゴリズムを使用して、チップの電源ネットワークの振る舞いをモデル化し、オンチップの抵抗、静電容量、インダクタンスなどの要素を考慮します。これにより、IC設計者は電圧降下が発生しやすい箇所を特定して、さまざまな動作条件下でのチップの振る舞いをシミュレーションできます。低消費電力ICを設計するには、設計時に電源ネットワークのあらゆる側面を考慮しながら、電圧の振る舞いを予測する必要があります。

詳細については、Ansys RedHawk-SCのページまたは「半導体パワーインテグリティ解析とシミュレーションの基礎」をご覧ください。