-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

-

產品系列

查看所有產品Ansys致力於為當今的學生打下成功的基礎,通過向學生提供免費的模擬工程軟體。

-

什麼是訊號完整性?

系統的訊號完整性 (SI) 測量電子訊號進入和離開電路之間的變化程度。對數位電子裝置而言,該訊號是一種電流,其電壓會隨時間在高低值之間變化。

訊號完整性對任何現代電子系統而言都是基本要素。業界使用「完整性」一詞,因為其意指遵守一套規則,維持不受損害的狀態,內容完整且未被拆分。如果訊號的波形因串擾、阻抗不匹配和遺失而與原始訊號有顯著差異,接收器將無法讀取訊號,產生訊號完整性問題。這就是為何訊號完整性工程 (包括分析與改善訊號完整性問題) 是設計積體電路 (IC)、IC 封裝與印刷電路版 (PCB) 的重要一環。

訊號速度增加以及印刷電路板(PCB) 和套件的尺寸縮小,讓訊號完整性問題更難處理。高速的數位訊號與較小的幾何設計,使訊號雜訊與失真更為明顯。然而,隨著難題增加,業界也越來越懂得如何應對,而且工程師可以利用工具的功能來定義、模擬和調整他們的電子系統。

這個波形的失真、雜訊、時間的偏移及振幅下降的情況,都是因為電子在驅動器與接收器之間流動時,材料中的電阻、移動電子產生的電磁場、其他電磁場引起的電流,及電路的電容等因素所引起的。在印刷電路板(PCB) 中,材料、建立電路的走線形狀、各層的擺放和厚度,以及層與層之間電流的傳遞方式都會影響這些效應。

我們也必須提到與此密切相關,並歸類為電源完整性的問題。訊號完整性與印刷電路板(PCB) 中的訊號傳真度有關,而電源完整性與提供給傳送和接收這些訊號之元件的電源品質相關。影響訊號完整性的阻抗、電感和衰減,同樣也會左右電源完整性。此外,變更其中一項完整性可能會對另一項造成負面影響,因此工程師在改良設計時,必須同時模擬並測量這兩個項目。

為什麼訊號完整性很重要?

如果沒有解決訊號完整性的問題,數位裝置可能會有重大問題。當訊號失真程度太大,使得通過電路的 0 或 1 無法正確接收,且二進位值錯誤時,就會產生最嚴重的問題。此外,出現嚴重雜訊或時間延遲時,裝置可能會故障。在當今高度複雜的印刷電路板(PCB)中,擁有數百條導線,只需一條存在訊號完整性問題的訊號路徑,就可能使整個電路板無法使用。

基於物理現實,將訊號經由電路傳送到另一端時,訊號不可能沒有變化。設計團隊對單一完整性分析基礎概念有深入瞭解、知道訊號完整性對現代電路設計的影響,並掌握確認和處理訊號完整性問題的方法,因此可將各裝置的完整性降至最低,並往更小的尺寸規格和更高的頻率發展。

訊號完整性分析的基礎概念

在材料之間移動的電子物理特性會影響訊號的完整性。Maxwell 方程式呈現了電荷和電流之間的關係、電流如何建立電磁場,以及磁場如何改變電流。

簡而言之,印刷電路板(PCB)中的互連被稱為數位訊號的傳輸線,像是天線、電阻和電容。訊號的特性、導電材料與電介質材料的材料特性、幾何及 印刷電路板(PCB)中電路與佈線層的相對位置,會決定 Maxwell 方程式所描述的物理強度與影響。

4 種訊號完整性問題

上述的基礎物理特性將訊號完整性問題分成以下四種:

1.電磁干擾 (EMI)/電磁相容性 (EMC)

在任何高頻電路中,正確的幾何與頻率組合會將走線或通孔變成可廣播訊號的天線,而該訊號可與同一 PCB 上或其他裝置中的其他電路、連接器或同一或附近裝置中的纜線進行耦合。當另一個電路接收到干擾時,電磁場中的能量會引發電流,並在該訊號中產生雜訊。廣播電磁波也會降低訊號的電壓,因為產生電磁場會消耗電力。設計師必須將干擾 (EMI) 降到最低,並確保正在開發的裝置與其運作所在的電磁環境相容 (EMC)。

2.串擾

串擾是另一種形式的電磁交互作用。相鄰的高速走線中的訊號與其電場和磁場耦合時,便會發生這個現象。不必要的訊號源自所謂的入侵走線,該入侵走線與相鄰的傳輸線路 (稱為受害走線) 上的訊號耦合。耦合的類型包括:

- 電容耦合:入侵電路的電場在受害電路誘發電壓所造成

- 電感耦合:入侵電路的磁場在受害電路誘發電壓所造成

- 電導耦合:兩種訊號的電流在接地面的返回路徑上耦合所造成

3.同步切換雜訊 (SSN) 造成的接地彈跳

當印刷電路板(PCB)的訊號接地在所有點並不一致時,會產生接地彈跳。這是多個電路同時改變其在高電位或低電位狀態之間的電壓,誘使接地面電壓增加,而造成的訊號完整性問題。這會導致低電位電壓,即二進位訊號中的 0,高於預期。有時候,彈跳高度足以造成錯誤讀取為高電位的問題。

4.阻抗不匹配

設計師必須考慮交流電 (AC) 電路的阻抗。阻抗是電流的電阻以及由電感和電容造成的電流變化。當電路上某處的阻抗改變時,就會發生阻抗不匹配的狀況。不匹配會導致部分訊號反射回來,然後來回傳播,直到衰減為止。除了將雜訊加入訊號之外,阻抗不匹配可能導致時序不確定性,稱為抖動。評估阻抗不匹配的標準工具是時域反射技術 (Time Domain Reflectometry, TDR)。TDR 會測量傳輸線路中的反射。

使用眼圖分析以圖表呈現訊號完整性

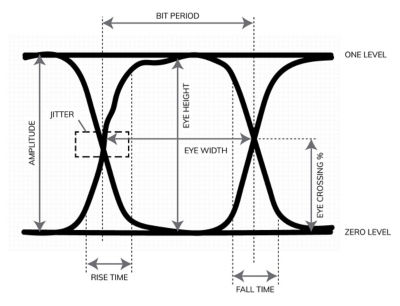

眼圖分析是探索訊號完整性最常用的工具之一。眼圖 (eye diagram 或 eye pattern) 是檢視一段時間內數位電路回應的方法。重複的訊號會輸入至所分析的電路中,並測量一段時間內的輸出訊號。資料的每個位元相互摺疊,X 軸是時間,而 Y 軸是振幅。由於輸入訊號為方形波,因此完美的電路會產生一個圖像,顯示上下兩條水平線以及中間兩條垂直線,水平方向上由資料的一個位元長度分隔,垂直方向上則由訊號的電壓差分隔。

但是完美電路不存在,因此圖形會轉變成類似眼睛的形狀。上述討論的訊號完整性問題,會表現為扭曲的直線。下圖顯示指出電路問題的典型數值。上升時間、下降時間、抖動和眼交叉百分比等數值會顯示訊號失真的情形,以及進入系統的雜訊對訊號的影響。

透過比較路由、幾何或材料變更前後的眼圖,設計師可以瞭解這些變更如何改善電路的訊號完整性。

開發此分析方法的最初目的,是為了利用示波器快速以圖表呈現電路的訊號完整性。現在,工程師會使用眼圖來檢視電路效能是否符合模擬的預測。設計師可以藉此快速探索變更,並在遠早於製作 PCB 原型之前便知道影響。

訊號完整性與積體電路 (IC)

本文著重於 PCB 的訊號完整性,但 IC 晶片的訊號完整性也至為重要。由於特徵尺寸較小且資料速率更高,在配置積體電路和定義互連時,考慮訊號完整性便更加重要。切換其他訊號的耦合效應是晶片發生訊號完整性問題的最大成因。此外,在晶片外部,做為套件互連的電線距離十分接近,足以遭受嚴重串擾的影響。

IC 晶片原型製作非常困難,因此在設計過程中要盡早使用模擬來建立訊號完整性和電源完整性模型,以找出並修正潛在問題。設計人員會使用這些工具驗證晶片,確認晶片是否會按照預期執行,然後再開始進行製造程序。

確認訊號完整性問題並改善效能的提示

為了避免高速數位設計發生訊號完整性問題,工程師可以採取的最重要步驟,是遵循公認的 PCB 設計產業規則。一些典型的規則包括:

- 指定走線之間的距離

- 避免走線寬度突然改變

- 保持在允許的邊角半徑內

- 避免走線和過孔殘樁

- 不在接地層中放置會使返回路徑中斷的不連續性

- 設計長度相同的差動對

- 降低電源面的阻抗

- 接地面的策略性定位以及 PCB 中每一層的正確厚度

- 避免在高頻率使用過孔

即使設計師的 PCB 佈局遵循所有設計規則,仍可能出現問題。平衡多項規則、製造限制、尺寸限制和成本問題時,也會出現挑戰。設計師通常會部署模擬,來識別這些問題並進行改良。

透過良好的參數設計和健全的模擬工具組,例如 Ansys SIwave™ PCB 和封裝電磁模擬軟體,以及 Ansys HFSS™ 3D 高頻模擬軟體,工程師就能快速進行交換研究以探索解決方案。

由於我們沒辦法看見、聽見或感受到電磁場或是走線中的電流,所以工程師利用模擬將出現的磁場和通量視覺化。此視覺化結果可讓工程師檢視電磁場的傳播、看見訊號返回路徑、將 PCB 和元件下方的升溫視覺化,及查看走線對之間的串擾。

訊號完整性的未來

訊號完整性的未來與最近的發展類似:資料速率提升、時脈速度加快,以及頻寬需求增加。封裝需求也會促使系統使用較小的 PCB、在 PCB 上封裝更多元件,並使用軟性 PCB 將元件彎折成複雜的形狀。為了滿足產業需求並提高市佔率,企業將引進新的製造流程,並嘗試不同的材料。兩者都會影響訊號完整性。

另一項在近期即將加速發展的趨勢,是佈局與模擬的緊密整合,在設計流程中強調更多物理原理。在建立 PCB 策略時,工程師將能探索自己設計的電磁場、電源完整性、散熱特性以及機械強度。

和其他領域相同,未來人工智慧 (AI) 將會在盡量減少訊號完整性問題中扮演重要角色。許多佈局工具已經使用較舊型的 AI 來執行設計規則,以在電路圖轉換成 PCB 佈局時佈設走線。新一代生成式 AI 工具將大幅改良設計和模擬工具的功能。

相關資源

讓我們開始吧

如果您面臨工程挑戰,我們的團隊將隨時為您提供協助。憑藉豐富的經驗和對創新的承諾,我們邀請您與我們聯絡。讓我們共同合作,將您的工程障礙轉化為成長和成功的機會。立即與我們聯絡,開始對話。