簡要規格

Ansys VeloceRF 讓您可以把多個裝置和傳輸線緊密封裝來進行裝置合成,製作最佳化的矽晶片佈局。在詳細配置之前分析任何數量的電感感應裝置之間的耦合,將減小設計尺寸並減少或消除防護環。

產品系列

查看所有產品Ansys致力於為當今的學生打下成功的基礎,通過向學生提供免費的模擬工程軟體。

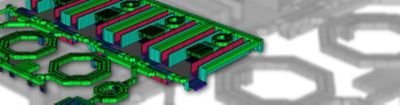

Ansys VeloceRF 大幅減少複雜螺旋裝置和傳輸線路合成與建模所需時間,藉此縮短設計週期。編譯電感器或變壓器幾何只需幾秒鐘,只需幾分鐘即可建模並進行分析。它與主要的 EDA 平台整合,可將準備好送交下線製造的佈局實例化。

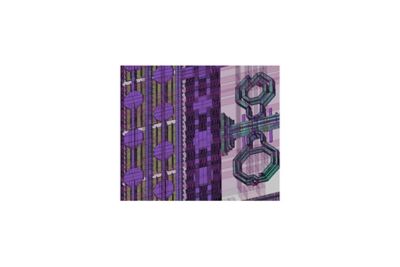

Ansys VeloceRF 讓您可以把多個裝置和傳輸線緊密封裝來進行裝置合成,製作最佳化的矽晶片佈局。在詳細配置之前分析任何數量的電感感應裝置之間的耦合,將減小設計尺寸並減少或消除防護環。

Ansys VeloceRF 大幅減少複雜螺旋裝置和傳輸線路合成與建模所需時間,藉此縮短設計週期。

電感器大小以及電感器到電感器的串音干擾可能會影響晶粒大小。Ansys VeloceRF 透過使用最佳化標準和幾何限制來幫助您設計更小的裝置。此外,它還會計算任意數量電感器之間的耦合,以更好地最佳化矽的基板面並最佳化電路環境中的電感器。Ansys VeloceRF 參數清理支援在電路環境中提供最佳的效能解決方案。經過晶圓代工廠驗證的準確度,可藉由獲得矽驗證的模型消除串音干擾故障,降低設計的風險。

Ansys VeloceRF 目前支援超過 200 個獨特的晶圓代工製程,並可與任何最小至 3 奈米的製程搭配,包括來自所有半導體晶圓代工廠,包括 TSMC、UMC、Global Foundry、TowerJazz 和 Samsung 等的 CMOS、BiCMOS、GaAs、SOS 和 SOI。該工具與主要的 EDA 設計平台以及任何 LVS 工具整合。

Ansys VeloceRF 只需幾分鐘即可合成並分析來毫米波螺旋裝置和傳輸線路。它會產生透過 DRC/DFM 驗證的裝置 (包括填料) 最小至 3 奈米。透過被動式、因果型 S 參數和極精簡的 RLCk 串接電路模型建立這些裝置的模型,可以作為 PCells/PyCells 提供,以實現最大的幾何靈活性。環境內最佳化可透過多重裝置和線路的平面配置緊密封裝來減少晶粒大小,以及減少或消除防護環。它利用預先定義的裝置構件材料庫支援高頻率,並支援任何數量的電感感應裝置進行耦合。

VeloceRF 提供矽上電感感應裝置的合成、建模、分析和最佳化的全面性綜合功能。

對 Ansys 而言,所有使用者皆能運用本公司產品非常重要,身心障礙者也不例外。因此,我們致力於遵循美國無障礙委員會 (第 508 節)、無障礙網頁內容規範 (WCAG)、自願性產品輔助工具範本 (VPAT) 當前格式等各項無障礙需求。

如果您面臨工程挑戰,我們的團隊將隨時為您提供協助。憑藉豐富的經驗和對創新的承諾,我們邀請您與我們聯絡。讓我們共同合作,將您的工程障礙轉化為成長和成功的機會。立即與我們聯絡,開始對話。