建立、驗證、部署和擴充混合式數位孿生模型

Ansys TwinAI 是採用 AI 增強模擬功能的數位孿生平台,能在雲端基礎架構環境中,為模擬引擎、作業系統和資料流驗證數位孿生模型。 它能讓您先行存取各種不同功能以模擬建立的數位孿生,透過混合式分析提高 Digital Twins 的準確度,同時精簡部署流程。

Ansys TwinAI 是採用 AI 增強模擬功能的數位孿生平台,能在雲端基礎架構環境中,為模擬引擎、作業系統和資料流驗證數位孿生模型。 它能讓您先行存取各種不同功能以模擬建立的數位孿生,透過混合式分析提高 Digital Twins 的準確度,同時精簡部署流程。

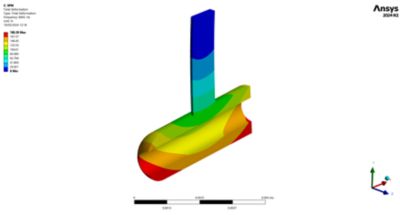

Ansys TwinAI 將物理模型的準確度,與尖端 AI 技術提供之現實資料的深入見解相互整合。Ansys TwinAI 提供無與倫比的出色準確度和速度,讓數位孿生徹底發揮完整潛力。

2025 年 1 月

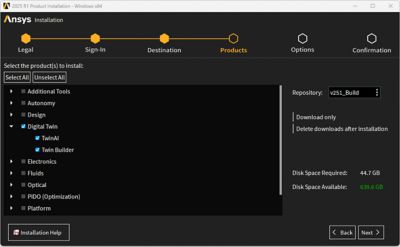

Ansys 2025 R1 透過混合式分析、擴充部署和全新功能強化其數位孿生能力,提升彈性和可用性。主要更新包括 Ansys Unified Installer、適用於降階模型 (ROM) 的可編寫指令碼 Python 介面,以及混合式分析後處理的增強功能。Ansys TwinAI 現在支援 SysML v2 程式碼片段匯出、功能表式說明、擴充的檔案匯出選項,以及 PyAEDT 和 PyTwin 的全新範例來簡化開發流程。

探索最新的 Ansys 更新內容,如何簡化模擬工作流程:Unified Installer 更易於使用、透過 Python 進行 ROM 編寫再升級、改善混合式分析後處理功能、從 TwinAI 匯出 SysML v2、TwinAI 直接協助存取、靈活匯出檔案,以及用於發展最佳化數位孿生的全新 PyAEDT/PyTwin 範例。

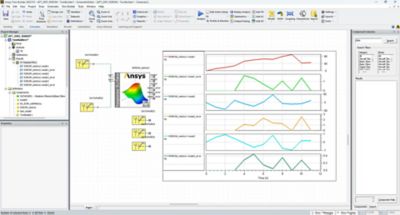

利用新的 Ansys 更新加強模擬準確性和效率:適用 ROM 的 SVD 基礎、預測錯誤及量化反應表面的不確定性、動態 ROM 建置器的 ROM 錯誤摘要,以及能夠從動態 ROM 軌跡識別其狀態,確保發展出功能強大的數位孿生。

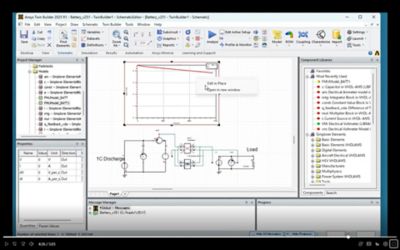

探索模擬強化後的進階功能:匯出用於 CS FMU 的 VHDL-AMS 元件、使用 SPICE 網表中的 Foster 網路散熱模型、改善 Maxwell 暫態共模擬及裝置特性描述、運用 SML 編譯器升級陣列型設計變數、存取 Modelica Standard 資料庫 4.0.0、支援 PSPICE MOSFET beta 測試版、更新版 VHDL-AMS 加密金鑰。

Ansys TwinAI 提供使用者圖形環境,以利匯入已產生的孿生,在需要執行不同作業系統時交叉編譯模型,並測試和驗證孿生模擬,確保其執行效能和準確度,均符合部署之前的預期。

Ansys TwinAI 具有廣泛功能,能獲得快速、準確、不斷進化的孿生。

TWINAI 資源與活動

2024 R2 帶來了嶄新功能,例如 Ansys 設計語言及全新改善 UI/UX的整合。使用者也可以在單一環境中建立降階模型作為 FMU,並從動態 ROM 初始化功能中獲得強化。

對 Ansys 而言,確保所有使用者皆能運用本公司產品非常重要,身心障礙者也不例外。因此,我們致力於遵循美國無障礙委員會 (第 508 條)、Web內容無障礙指南 (WCAG)、與目前自願產品無障礙工具範本 (VPAT) 的格式等各項無障礙要求。

如果您面臨工程挑戰,我們的團隊將隨時為您提供協助。憑藉豐富的經驗和對創新的承諾,我們邀請您與我們聯絡。讓我們共同合作,將您的工程障礙轉化為成長和成功的機會。立即與我們聯絡,開始對話。