簡要規格

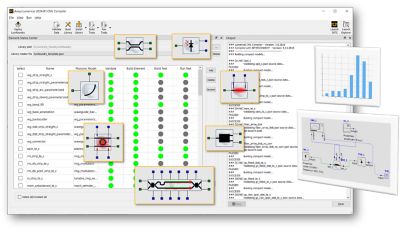

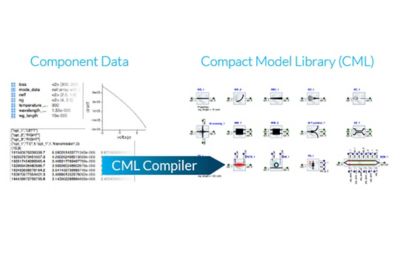

Lumerical CML Compiler 提供了一種有效的方法,從測量和/或模擬資料的單一來源來建立高品質 INTERCONNECT 和 Verilog-A 光子緊湊模型。

自信建立和維護 CML

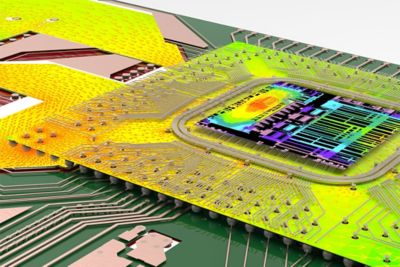

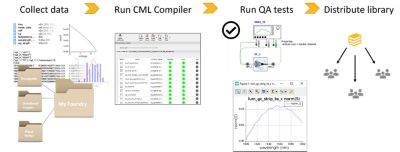

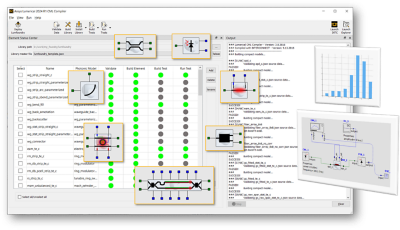

運用 Lumerical CML Compiler 經實證的可靠性,有效率地建立緊湊模型庫 (CML)。此軟體可從單一資料來源自動建立 INTERCONNECT 與 Verilog-A 光子緊湊模型庫,並進行校準、維護和 QA 測試。來源資料可能來自實驗性測量、2D/3D 物理模擬或兩者的組合。

Lumerical CML Compiler 提供了一種有效的方法,從測量和/或模擬資料的單一來源來建立高品質 INTERCONNECT 和 Verilog-A 光子緊湊模型。

2025 年 1 月

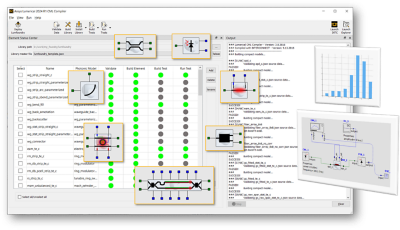

Ansys 2025 R1 擴展了光子設計能力,透過自訂 Verilog-A 模型建立獨特元件,並引入光纖陣列以進行精確的晶片對光纖耦合損耗建模,同時支援蒙地卡羅良率分析。

此模型允許 CML Compiler 使用者為任何目前還不受 CML Compiler 支援的獨特的、主動或被動的自訂元件建立 Verilog-A 光子模型。使用者可以編寫自己的 Verilog-A 程式碼,以定義該元件的輸入與輸出關係。

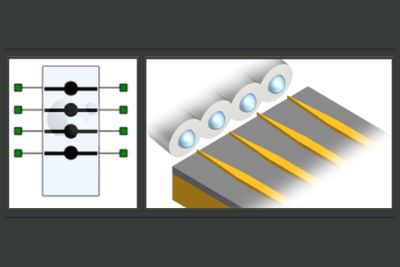

新的光纖陣列可讓使用者對晶片與光纖之間的耦合多餘損耗進行建模,並支援陣列中任意數量的 Pcell 參數與光纖。此外,統計式模型支援蒙地卡羅掃描以進行良率分析,並將統計參數之間的相關性列入考量。

功能

CML Compiler 可從測量和模擬結果的單一資料來源自動建立 INTERCONNECT 與 Verilog-A 光子緊湊模型庫 (CML),並進行維護和 QA 測試。

CML Compiler 簡化了準確光子緊湊模型的構建,適用於光子 PDK,支援光子積體電路設計。

Lumerical 技術長 James Pond 博士帶領我們了解 CML Compiler 的起源和開發過程,以及在 OFC 2020 中展示的新統計分析和模擬功能。

對 Ansys 而言,確保所有使用者皆能運用本公司產品非常重要,身心障礙者也不例外。因此,我們致力於遵循美國無障礙委員會 (第 508 條)、Web內容無障礙指南 (WCAG)、與目前自願產品無障礙工具範本 (VPAT) 的格式等各項無障礙要求。

如果您面臨工程挑戰,我們的團隊將隨時為您提供協助。憑藉豐富的經驗和對創新的承諾,我們邀請您與我們聯絡。讓我們共同合作,將您的工程障礙轉化為成長和成功的機會。立即與我們聯絡,開始對話。