-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

-

產品系列

查看所有產品Ansys致力於為當今的學生打下成功的基礎,通過向學生提供免費的模擬工程軟體。

-

什麼是先進半導體封裝?

先進半導體封裝是將多個半導體晶片結合為單一電子封裝的一系列製造程序。這種方法可提升功能並降低功耗和成本。

傳統封裝方式就像是在一片土地上建構單層建築。先進封裝可讓您將數棟建築物放在較小的土地上,並與橋樑、升降井和隧道相連。若企業能有效運用這些技術,就能在快速成長的半導體市場中獲得競爭優勢。

先進封裝中最常用的技術為 2.5D、3D-IC、異質整合、扇出型晶圓級封裝和系統級封裝。每種技術都是不同的方法,用於從晶圓取得單一晶片,並將其與其他晶片放在以塑膠、金屬或玻璃包覆的單一電氣連接組件中 (封裝)。建立後,封裝會連接到印刷電路板或彈性膠帶,並放入電子裝置中。

先進半導體封裝的優點

當半導體技術遇到物理定律時,將更多電晶體放入更少空間的技術也變得費力。數十年來,微電子產業一直將 Intel 共同創辦人 Gordon Moore 的預測,亦即晶片中的電晶體密度每兩年就會倍增 (稱為摩爾定律),用於引導其投資與規劃,以跟上發展腳步。這將每一代晶片往更小的特徵尺寸與更高的密度推動,使裝置中的電氣連接 成為效能瓶頸。 .

先進封裝是設計師克服此限制的強大方法。它們可以透過在三個維度中排列多個晶片,並在晶片之間與過渡的積體電路中直接建立連接,以消除瓶頸並降低成本。另一項優點是將具有不同功能的晶片放在附近,如此可降低功耗、提高速度,並將多功能裝置簡化為單一封裝。

這種單一封裝的外型規格也能將整合從涉及多個元件的後置處理步驟,移轉到半導體製造廠區 (也稱為晶圓廠) 的前端步驟,藉此降低製造、運輸和庫存成本。這種方法也能大幅降低封裝人力成本,不需要在人力成本較低的地點另外設置封裝設施。

使用以先進半導體封裝所製作之模組的裝置應用

隨著人們對於運算能力和記憶體的需求日益增加,以儲存人們建立的所有資料,因此需要更有效率、更便宜的微電子裝置。更精密且功能更強大的消費性電子元件也營造出以更低的功耗,在更小型的封裝中具備更強大功能的市場。越來越多裝置變得更聰明,增加了測量 (感應器)、匯入資料、計算 (處理器)、儲存資料 (記憶體) 或匯出資料的元件。先進封裝可協助產品將每個功能的多個執行個體結合為單一模組。

汽車產業是其中成長最快速的領域之一。具效能、效率和安全性的先進系統,加上不斷增加的感應器數量,提高了對以先進封裝製造更強大、更有效率、更便宜的電子模組的需求。

物聯網 (IoT) 裝置是產品設計師想要將多種電子功能整合於單一部分,以新增至其電子設計的另一個例子。以先進封裝技術打造的解決方案可簡化組裝自動化及 PCB 複雜性,同時提高效能並降低成本與功率需求。

先進封裝有助於實現人工智慧 (AI) 和高效能運算 (HPC) 的密集運算需求。這種方法能以更小、更省電的組態提供更多功能。AI 和 HPC 的硬體供應商 (如 NVIDIA) 已建立先進封裝供應鏈。他們 選擇 Intel 和 TSMC 的先進封裝功能,生產所需的多功能模組以提升效能,同時還能控制功率需求和成本。

先進封裝元件與技術

先進半導體封裝採用多種技術,讓封裝中的 IC 晶片更有效率地結合。

如要瞭解先進封裝,不錯的著眼點是查看其元件,以及半導體晶圓廠所採用的各種先進封裝技術。

元件

- 小晶片:針對特定功能最佳化的未封裝離散裸晶,在封裝層級結合其他小晶片與多功能 IC 晶片。

- 裸晶:這是一塊從大型晶圓切割的半導體材料區塊,其中包含專為執行一或多項功能而設計的電路。 當裸晶連接到基板或其他裸晶時,它們會變成晶片。

- I/O 墊或凸塊:在晶片表面上的導電區域,用於將訊號傳送至晶片,或從晶片中輸出訊號。

- 互連:連接兩個或更多電路元件以在其中傳輸電流的結構。通常是連接一或多個裸晶的薄型結構。

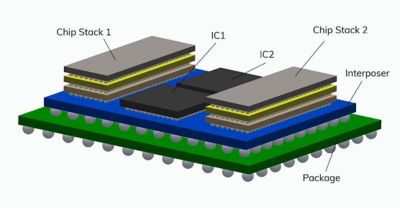

- 中介層:一或多個晶片和一個基板之間的一層材料。在先進封裝中,材料可以是矽晶或玻璃型。

- 印刷電路板 (PCB):剛體或彈性的平面結構,具多層電路,在電子系統中以電氣方式連接元件。剛體結構通常是由 FR4 製成,而彈性結構則是由聚醯胺製成。

- 重新佈線層 (RDL):在一或多個裸晶下方的額外金屬化層,含有內部導電路徑,可建立更有利的 I/O 墊。

- 焊錫球:用來連接半導體封裝中元件的小焊錫球。其尺寸會因連接的元件而異。

- 基板:包含電路的平面元件,可在封裝中以實體和電氣方式連接其他元件。IC 基板是半導體材料的一層,以及由 FR4 或聚醯胺製成的層壓基板。

- 系統單晶片 (SoC):將所有電腦或電子系統功能整合至單一晶片的 IC 晶片。

- 矽穿孔 (TSV):矽晶圓或裸晶頂部與底部之間的電力連接。這可將薄半導體材料轉變為元件之間的互連。

- 焊線:裸晶與基板之間或多個裸晶之間的金屬線。這種在封裝中連接元件的方式相對便宜,在傳統封裝中是主流。

技術

2.5-D 堆疊使用中介層搭配 TSV 將多個晶片連接至封裝,而 3D 堆疊則使用 TSV 作為垂直堆疊裸晶的設計。

- 2.5-D:2.5-D 技術不是將多個裸晶連接到 IC 基板,而是使用裸晶與基板之間的中介層。中介層使用 TSV 將訊號傳遞通過中介層。

- 3D-IC:一種將多個裸晶相互疊放的方法。TSV 會連接裸晶。

- 扇出型晶圓級封裝:從晶片上的高密度 I/O 墊轉換為基板上的較大球柵陣列的 RDL。

- 系統級封裝 (SiP):2.5D 或 3D-IC 技術用於產生完整的電腦或電子裝置封裝。SiP 可結合多個裸晶,在單一封裝中達到相同行為,而非放置系統單晶片解決方案所需的所有 IC。

先進半導體封裝的挑戰

從打包行李箱到建立最新的 GPU 模組,封裝的目標是盡可能有效率地在您的空間中裝入所有必需物品。對於先進半導體應用,您還必須處理電源完整性、訊號完整性、熱完整性,以及機械應力問題,同時維持成本目標。

互連

封裝中的每個晶片都必須連接,並連接至將模組連接至其他電子裝置的 I/O 墊。封裝中必須設計導電路徑,例如互連、TSV 或電線。由於它們會帶有訊號,因此必須檢查每個路徑,以確保其訊號不會互相干擾,也不會過熱。

功率

功率效率是驅動市場差異化的因素。客戶想要用較少的功率來完成更多工作,因此封裝設計師必須開發組態,並運用減少功耗與損耗的技術。

熱

施加電流時,封裝中的每個元件都可能產生熱能。封裝需要散熱管理解決方案,運用組態和材料將熱蓄積降到最低,將熱能從元件轉移出去,以及瞭解它如何影響所使用的裝置。

堅固耐用

當封裝發熱及冷卻時,材料會膨脹和收縮。設計師必須使用各種材料與互連技術,以確保每項材料的膨脹差異,以及重複膨脹與收縮不會導致任何互連或晶片故障。瞭解焊錫球疲勞與封裝設計也必須能承受汽車、IoT 和航太等應用的嚴苛環境的磨損與拉扯。

成本

在競爭激烈的半導體產業中,成本是主要的驅動因素。作為後端程序封裝,傳統的晶片封裝可能需要大量人力,而且包含運輸成本。先進封裝程序必須利用自動化,並將封裝移作前置程序的一部分,包括整合式測試。設計師經常會利用最佳化工具,以成本為考量,聰明地選擇合適的選項。

先進半導體封裝的未來

在整個半導體供應鏈中,各公司正在發展藍圖,包含更先進封裝、更高的效能,以及更低的成本。Yole Intelligence 最近的研究指出,2022 年的先進封裝佔這個 920 億美元產業的 48%。根據報告預測,到了 2028 年,該市佔率將成長至這個 1,360 億美元產業的 58%。

新一代的封裝製造必須運用新的材料、更優異的自動化能力與創新的技術,以滿足對省電效率與經濟實惠封裝、更小巧的晶片設計,以及系統單晶片應用日益增長的需求。

國家/地區和公司之間的封裝生態系統競爭將會非常激烈。2023 年的《晶片法案》在國家先進封裝製造計畫的經費金額達 30 億美元。業界領導者 Intel、TSMC 及 Amkor 分別在 2023 年宣布價值 35 億 、29 億以及 20 億美元的投資,以開發新的先進封裝設施。

除了製造工廠的技術以外,工程師還會尋找更好的軟體工具,以支援可整合至設計工作流程的特定封裝技術。例如 Ansys、Microsoft 和 TSMC 最近協同合作,開發 2.5D/3D-IC 封裝適用的雲端應力模擬工具組。

相關資源

讓我們開始吧

如果您面臨工程挑戰,我們的團隊將隨時為您提供協助。憑藉豐富的經驗和對創新的承諾,我們邀請您與我們聯絡。讓我們共同合作,將您的工程障礙轉化為成長和成功的機會。立即與我們聯絡,開始對話。