-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

-

產品系列

查看所有產品Ansys致力於為當今的學生打下成功的基礎,通過向學生提供免費的模擬工程軟體。

-

ANSYS 部落格

October 10, 2019

什麼是串擾?電磁挑戰和趨勢

什麼是串擾?

串擾現象是指來自某一電路或傳輸線路的訊號,會干擾相鄰電路或線路的情況。每個訊號都會產生不同的電磁 (EM) 場。當這些訊號或電路彼此鄰近時,其 EM 場會重疊。此干擾會導致不必要的訊號耦合,進而造成串擾。串擾可能會發生在電子系統中,例如印刷電路板 (PCB)、積體電路 (IC) 和通訊纜線等。

工程師再也不能忽視電磁串擾了。他們必須了解電磁串擾是什麼、如何找出,以及如何修正電磁串擾。

造成干擾的 EM 訊號稱為入侵者,受串擾影響的 EM 訊號則稱為受害者。串擾會透過兩種機制引發:

- 電場引起的電容串擾。

- 磁場引起的電感串擾。

串擾範例

印刷電路板 (PCB):PCB 涉及複雜的電路設計,其中多個走線會在彼此附近運作。高頻率訊號通過走線時,會因電容或電感耦合而在相鄰的走線中引發電壓,進而引發串擾。

積體電路 (IC):不同的組件和互連均緊密封裝在積體電路中。當 IC 某一部分產生的電磁雜訊 (因電晶體切換所致) 與相鄰元件耦合時,就會導致串擾,降低效能。

通訊纜線:像是乙太網路纜線等通訊纜線之中,是由多個雙絞線傳輸資料。如果絞線不夠緊密或纜線屏蔽不良,那麼來自某一雙絞線的訊號可能會串擾至相鄰的雙絞線,導致資料損毀或訊號品質降低。

高速資料傳輸:在 HDMI 或 USB 纜線等高速資料傳輸中,訊號可能會因為高頻率而相互干擾。此干擾會導致串擾並降低訊號品質。

無線電頻率 (RF) 系統:在無線電頻率 (RF) 系統中,相鄰的天線或 RF 傳輸線路之間可能會發生串擾。這可能造成訊號干擾,降低系統的有效性。

SOC 中的串擾

工程師若開發出忽略串擾的系統單晶片 (SoC) 架構,將承受重大風險。串擾可能產生電子設計錯誤,而這會導致延誤上市和成本超支。

辨識 EM 串擾的挑戰

若要理解 EM 串擾分析的複雜性,工程師可以拿這個問題來對比電容耦合。

電容耦合在近距時較強,遠離時較弱。因此,工程師可以安全地忽略相隔很遠的訊號線路之間的電容耦合。相較之下,在相對較遠訊號之間的電感磁耦合則無法忽略。

很多時候,我們很難判斷電磁串擾是否為問題根源。

EM 串擾較具挑戰性。首先,此問題的症狀不會出現在單一指標中,例如時序失敗等。串擾反而通常會以衰退的形式,呈現在設計不同的某些關鍵效能條件中。因此,辨識問題是否為串擾是第一項挑戰。

而讓情況更複雜的是串擾通常涉及在數位、類比和無線電頻率 (RF) 區塊之間的不必要耦合。任一方都可能是入侵者或受害者。

在不同的設計中,需要以不同的方式辨識 EM 串擾,並對其進行除錯與解決問題。傳統的解決方案需採用架構或軟體技巧,來預防會觸發問題的運作模式。然而,隨著設計的複雜度和速度不斷增加,這種方式在財務上和技術上都變得不可行。

EM 串擾建模的挑戰

為了準確為 EM 串擾建模,工程師必須分析極其複雜的物理結構範圍並加以建模,這些範圍包括:

- 相關線路

- 引發串擾的周圍結構

- 電源和接地佈線層

- 塊狀矽基板

- 封裝層

- 焊墊/凸塊墊

- 佈線層

- 密封環

- 金屬填料

- 去耦電容

由於需要包含上述所有元件,EM 串擾建模過程相當複雜。

這些結構大多有複雜的實體佈局,需要大型網格來模擬電阻、電容、電感、耦合電容和互感。

增加串擾模型尺寸的第二個建模因素,是工程師無法透過將焦點限制在設計中的小型定界框內,以分析 EM 串擾。評估電氣電容耦合時,可妥善地分析鄰近的受害訊號。然而,磁場可能會沿著大規模的迴圈移動,此迴圈可能是在鄰近受害訊號的區域外部形成,或是環繞著晶片的整個佈局。

此外,我們很難限制 EM 串擾工具所產生的模型尺寸,因為此模型需要將會導致串擾問題的所有線路,以及可能會對電路效能產生影響的所有線路和結構納入其中。

為了在下游開發中發揮作用,串擾模型必須:

- 在積體電路通用模擬程式 (SPICE) 中快速運算

- 在 SPICE 環境內的各種非線性和雜訊模擬中運作

- 存在於可跨越區塊界線或裸晶的資料庫內

鑑於串擾模型的典型尺寸和複雜性,我們很難滿足這三個要求。

對於 SoC EM 串擾分析的需求逐漸興起

EM 串擾對工程師來說是一大考量,因為需要透過電子系統來增加頻寬並縮減尺寸。這讓高速電路和高頻寬通道更加靠近。

隨著電子設備變得越來越小,串擾的問題也變得越來越顯著。

此外,持續增加的內部時脈頻率 (5 到 10 GHz) 以及資料速率 (10 Gbps 以上),也造成更多串擾問題。

簡而言之,高速和小型電子設備會產生串擾;消費者需求創造了 SoC 的趨勢,因此我們無法再忽略寄生電感和電感耦合。

容易發生串擾的 SoC 架構

許多架構和應用的設計趨勢都會引發串擾。

例如,EM 串擾會受到頻率影響。但是,工程師無法為了簡單的相關頻率而分析 EM 串擾。

例如,具有快速上升和下降時間的時脈訊號包含重要的諧波頻率成分。因此,以 10 GHz 運作的時脈具有以 50 GHz 運作的五次諧波頻率成分。

同一系統上有多個乙太網路通道,可能會變成一場串擾夢靨。

然而,鎖定晶片內時脈頻率 25 GHz 的工程師,就必須思考要如何為三次諧波安全建模,此諧波所在的頻率就是微波頻率。

EM 串擾會影響訊號幅度或雜訊位準。因此,由於 SoC 應用中的低功耗趨勢,促使訊號電壓位準降低,對雜訊的敏感度則會增加,而讓串擾的影響進一步加劇。

乙太網路、光纖通道和周邊元件互連 (PCI) 也可能是串擾的來源。為了達到高資料速率,這些匯流排採用平行運作的多個序列通道。例如,100 Gbps 乙太網路可能使用 10 個通道,且每個通道都以 10 Gbps 運行。當許多高速序列通道位於單一系統中時,每個通道都可能成為入侵者或受害者,這是一場真正的串擾夢魘。

其他會增加 EM 串擾可能性的架構趨勢包括:

- 一個 SoC 上有多個高速類比模擬塊

- 像是鎖相迴路 (PLL) 和壓控振盪器 (VCO)

- 同一晶片上有多個高速時脈網路

- 時脈不需要高頻運行,以 10 GHz 運行的受害時脈會受以 2 GHz 運行的入侵時脈所影響。

- RF 或高速類比模擬塊與高速數位模擬塊相鄰

- 共用接地線路和矽基板不能接地使用。

- 矽基板仍是區塊間的關鍵雜訊傳播通道。

- 晶圓廠插入的密封環和切割道

- 訊噪容差很小的低功率設計

- 可透過串擾突波設置的靈敏控制/復位訊號

- 整合型扇出晶圓極封裝技術

- 多裸晶相鄰會增加發生 EM 串擾的可能性。

- 多裸晶相鄰會增加發生 EM 串擾的可能性。

串擾的解決方案

SoC 整合會將高速數位電路、類比和 RF 區塊緊密地放在一起,而讓這些元件的內部和各個模塊之間會出現許多產生串擾的機會。

大多數的電子設計自動化 (EDA) 工具都是針對特定設計類型打造而成,例如數位、類比或 RF 元件設計。但是串擾並不受這些界線限制。

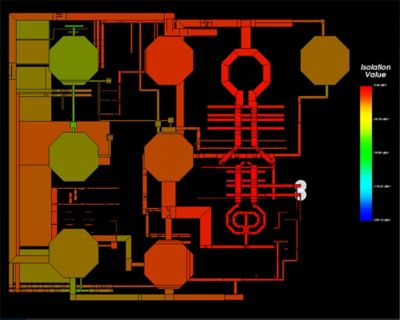

Ansys Pharos 可以協助工程師辨識串擾。

IC 設計工程師應可在簽核階段期間預測耦合效應。設計師可使用 Ansys RaptorH IC 準確預測電磁耦合效應,並在設計階層的不同區塊中,輕鬆擷取未知的串擾。

若要深入瞭解串擾,請閱讀以下文章:針對串擾將高速序列連結最佳化。