-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

-

產品系列

查看所有產品Ansys致力於為當今的學生打下成功的基礎,通過向學生提供免費的模擬工程軟體。

-

身為經驗豐富的半導體工程師或設計師,想像一下若您為新的積體電路 (IC) 設計出對稱網路佈局,但在佈局後的 SPICE 模擬中卻發現虛假的電子不匹配問題。這種違反直覺的結果會讓您回到設計中檢查是否有不對稱的地方,但您完全找不到。這究竟是怎麼回事?

其實這種虛假的電子不匹配效應是寄生電阻網路節點上寄生耦合電容器的分布差異所造成的。而這又是寄生萃取和寄生萃取工具的假影所導致的。

我們將在本文中為您提供實用的建議,以識別這些虛假的不匹配情況,並與佈局差異所造成的真實不匹配問題區分開來。Ansys ParagonX 寄生萃取軟體可協助您避免這些假影,並確保佈局後模擬和 IC 設計流程的可靠度。

IC 設計中的裝置和網路匹配

許多類比和射頻 (RF) 積體電路都依賴裝置和網路匹配的概念。1,2此類電路的範例包括 StrongARM 閂鎖、感測放大器、差動對、電流鏡、多相時脈等眾多例子。匹配的網路和裝置可為您提供一些彈性空間,確保電路能夠處理不可避免的製程變化。

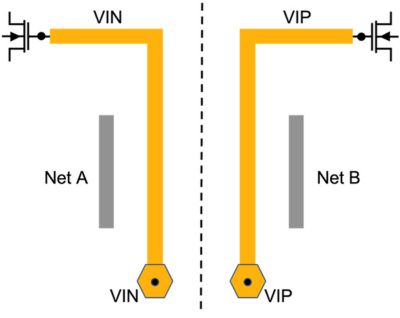

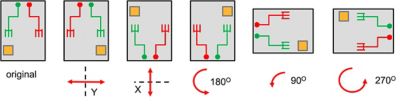

為了實現完美的網路匹配,設計師透過在 X 或 Y 軸翻轉設計,或移動或旋轉單元的方式,來建立對稱佈局,如圖 1 所示。

但是,由於設計規則、電線可繞性和幾何形狀的限制,很難實現完美的對稱性和匹配。這就是為什麼必須執行寄生萃取以驗證匹配,然後進行佈局後電路模擬,作為標準佈局後設計流程的一部分。若模擬顯示良好的預期結果,則表示您已達到最佳的對稱性和匹配。若測量到的訊號中有些許偏差、不匹配或差異,表示匹配程度不夠好,佈局需要被改進。

真正的問題

以下是真正的難題所在:即使網路完全對稱且匹配,佈局後模擬也經常會顯示電子行為的差異。典型的情境是,當兩個網路的電容和電阻相當匹配,但 RC 延遲不匹配的程度較大,以 τ (小寫希臘文 tau) 表示。常識和基本的物理學知識指出,若電容和電阻匹配,則延遲也應匹配。在這種情況下,延遲不匹配是違反直覺的。

圖 1.匹配的網路 VIN 和 VIP 的佈局。輸入埠為 VIN 和 VIP,而目標點是 MOSFET 的閘極。網路及其環境以對稱方式建立,以確保寄生電阻、耦合電容和 RC 延遲匹配。

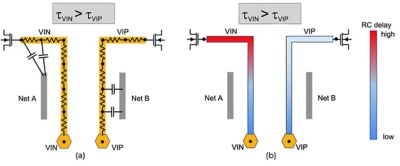

圖 2.(a) 寄生元件 (電阻和電容) 圖示。請注意非對稱性,即網路 VIN 和 VIP 耦合電容分佈的差異。(b) 網路佈局上的 RC 延遲圖示。由於耦合電容集中在網路 VIN 的遠端 (形成 VIN 埠) 和 網路 VIP 的近端,因此 VIN 的延遲大於 VIP 的延遲。

其實問題在於寄生萃取軟體。具體而言,延遲不匹配的根本原因與寄生萃取工具如何在電阻網路的節點上分配耦合電容有關。由於某些原因,耦合電容的分佈非常不對稱,如圖 2 所示。

這種非對稱性最可能的原因是萃取工具所使用的運算幾何演算法的各向異性。這些演算法 (例如掃描直線或橫越多邊形邊界) 具有偏好的方向,例如左右、上下,或順時針和逆時針。因此,演算法將佈局視為平面系統,而非 3D 系統。這會導致系統失去理論上可用來轉換偏好方向的自然階層和單元轉換特性。

為了研究此假設,我們透過分析佈局後網表並針對數個 GDS 檔案執行佈局後模擬,進行了一系列實驗。原始 DSPF 檔案用於參考,並與透過各種轉換取得的 DSPF 檔案進行比較,這些轉換包括 X 軸和 Y 軸的對稱反射,以及旋轉 90 度、180 度和 270 度。對稱轉換的結果如圖 3 所示。

圖 3.(a) 原始和 (b) 翻轉 GDS 檔案的 RC 寄生。網路 VIN 和 VIP 的耦合電容分佈在 (a) 和 (b) 案例中是反向的。左右邊網路耦合電容的分佈相同,如 (a) 和 (b) 案例所示。

如預期,原始的左邊網路和翻轉佈局的耦合電容分佈相同。右邊網路的分佈也是相同的。然而,由於網路 VIN 和 VIP 從原始佈局變為翻轉佈局,因此案例 (a) 的網路 VIN 耦合電容分佈現在變成案例 (b) 的網路 VIP 耦合電容分佈,反之亦然。

電容分佈的這種變化與 VIN 和 VIP 上的模擬 RC 延遲有很高的相關性。在案例 (a) 中,網路 VIN 的 RC 延遲 τ 比 VIP 大,但在案例 (b) 中小於 VIP 上的 RC 延遲。同樣地,我們也觀察到佈局後電路模擬的差異,在案例 (a) 中顯示網路 VIN 的轉換時間大得多,在案例 (b) 中顯示的轉換時間則比網路 VIP 的轉換時間小得多。這顯示對稱網路 VIN 和 VIP 之間的電子不匹配是寄生萃取工具的假影,如上所述。

當然,如果網路 VIN 和 VIP 的耦合和 RC 延遲差異在執行佈局轉換後沒有改變跡象,則這種差異是真實的佈局不匹配所導致,需要在佈局上加以修改。

透過寄生電阻網路的耦合電容器分佈

此實驗可能是首次有團體研究寄生萃取假影與對稱佈局耦合電容的各異向性非對稱分佈有相關。

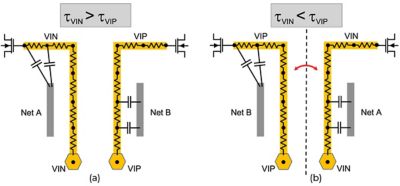

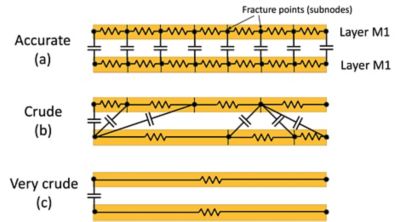

在不同的設計、技術、晶圓廠和三種主要寄生萃取工具中,皆觀察到虛假的不匹配效應。虛假各向異性的嚴重性因不同的萃取工具而異。這可能是因為三種寄生萃取工具的耦合電容器分佈品質不同,範圍從準確到粗糙到非常粗糙,如圖 4 所示。

每個寄生擷取工具都會嘗試最小化寄生 RC 網路的大小,以實現快速佈局後模擬時間 (適用於 SPICE、EMIR、時序和其他工具)。網表大小 (模擬時間) 和準確度之間總是有權衡。不同的寄生萃取工具會以不同的物理感知層級和不同的準確度來完成這項工作。

圖 4.寄生電阻網路節點上耦合電容的分佈。案例 (a) 最準確,案例 (b) 較不準確,而案例 (c) 非常粗糙。

模擬和分析結果

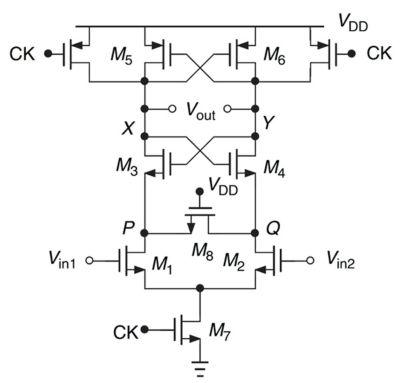

在 5 奈米 FinFET 技術中實作的 StrongARM 閂鎖3 (見圖5) 佈局後 SPICE 模擬顯示,裝置 M1 和 M2 的轉換時間不匹配,為 ~500 fs,遠高於此不匹配的上限規格 (~30 fs)。佈局相對較小,其目視檢查並未發現任何不對稱。設計師和佈局工程師對佈局進行了幾次迭代,試圖消除模擬中的不匹配現象。這花了他們兩個多星期的時間,但沒有成功。

沿著 Y 軸翻轉佈局會導致佈局後的網表顯示不匹配與相反符號:–370 fs。這個結果是一個明確、令人信服的論點,即 +500/-370 fs 的不匹配是寄生萃取工具的假影所造成的。

使用 ParagonX 電子設計自動化 (EDA) 工具分析網路不匹配,確認網路 in1 和 in2 之間的 RC 延遲差異較大,超過 15%。這種差異會變更原始和翻轉佈局的符號。隨後使用 ParagonX 軟體將耦合電容視覺化,進一步證實其分佈有強烈的不對稱性。(基於第三方的機密性原因,本部落格無法展示這些圖表。)

有趣的是,網路 in1 和 in2 的電阻和網對網耦合電容匹配準確度非常高。電阻匹配程度優於 0.05%,耦合電容匹配程度優於 0.2%。這是我們在許多佈局後的網表中觀察到的常見效應。雖然匹配網路上的電容和電阻非常接近,但由於本部落格中討論的影響,RC 延遲可能會大不相同。

據信,0.2% 的電容差是基於規則 (基於模式匹配) 的電容萃取不準確所致。使用由使用者控制的準確度目標設定,以隨機為基礎的場求解器 (FS),可以獲得更高的電容萃取準確度。對於電容匹配 (或 SAR ADC 中電容器陣列的二進位或非二進位加權) 對電路操作至關重要的網路,建議始終使用選定的網路 FS 萃取模式。

討論結果

圖 5.StrongARM 閂鎖示意圖。為了 RC 延遲,網路 in1 和 in2 應匹配。

佈局後電路模擬被視為分析和模擬客製電晶體層級 IC 設計的黃金標準。我們觀察到的虛假不匹配效應會導致一個有趣的問題:佈局後模擬的準確度如何?顯然,佈局後模擬準確度不可能高於寄生萃取工具的準確度。雖然電容和電阻萃取通常相當準確,但耦合電容在寄生電阻網路節點上的粗糙分佈,可能會導致暫態和 AC 模擬中出現誤差 ~500 fs (或更多)。這項發現可能會對精確和高速類比設計、時序分析和其他應用的 SPICE 模擬之可靠度和準確度產生重要影響。至少,業界需要建立偵測、除錯、解決或規避此問題的方法。

同樣重要的是,萃取假影引起的虛假不匹配問題可能會掩蓋真實的佈局和電子不匹配,這是由匹配網路的佈局和環境差異所造成的。在有虛假不匹配問題的情況下,要偵測真實的不匹配會變得很困難,甚至不可能。此外,如果虛假和真實的不匹配恰好相互抵消,則真實的不匹配可能會看起來像零或很小的不匹配,這也是高風險因素。

實際建議

請考慮以下建議:

- 對於電路設計師和佈局工程師:

a. 多加注意一般的不匹配問題,特別是不正確的寄生萃取引起的虛假不匹配。

b. 提高對這些效應的認識。要求 EDA 工具供應商提高準確度,並消除與耦合電容器分佈相關的寄生萃取中的此類假影。

c. 使用場求解器對匹配網路進行準確、受控的電容萃取 (如果電容匹配至關重要)。

d. 使用 ParagonX 軟體或其他 EDA 工具,主動檢查並驗證佈局後網表中的網路與裝置匹配,除錯此類問題,並改善佈局匹配。

- 對於 EDA 工具供應商:提高寄生萃取工具的準確度,尤其是提高耦合電容器分佈的品質。

- 對於晶圓代工廠:對與網路匹配和耦合電容器分佈品質相關的寄生萃取工具執行更全面的驗證和鑑定。

- 對於 EDA 研究人員:想出更好的演算法和方法,以提高佈局後網表的準確度,而不會使其規模變得太大。

- 對於所有人:檢查設計流程中是否有由寄生萃取引起的虛假不匹配:

a. 透過將對稱轉換套用至原始佈局來建立佈局 (參見圖 6),例如:

i. 沿著 X 軸翻轉。

ii. 沿著 Y 軸翻轉。

iii. 旋轉 180 度,旋轉 90 或 270 度 (如果 DRC 允許)。

b. 執行寄生萃取。

c. 使用 ParagonX 軟體比較原始和轉換後佈局的佈局後網表。

i. ParagonX 軟體能比 SPICE 更快、更容易地偵測和除錯不匹配問題。

d. 如果無法使用 ParagonX 軟體,請使用佈局後 SPICE 模擬或其他分析工具 (STA 等) 來比較兩個佈局後的網表。

e. 若有表示存在虛假不匹配的重大差異:

i. 對佈局進行目視檢查 (如果可能)。

ii. 向寄生萃取工具供應商和晶圓廠報告發現結果。

圖 6.有助於識別虛假網路不匹配的佈局轉換。電子特性對於這些轉換來說是不變的,因此寄生電容、電阻、延遲、裝置和 SPICE 模擬也應該是不變的。

深入瞭解 Ansys ParagonX IC 佈局寄生分析和除錯軟體如何協助您解決 IC 設計中的虛假電子不匹配問題。

參考資料

[1]《The art of analog layout》, 2nd ed., A. Hastings, Prentice Hall, 2005.

[2]《CMOS IC Layout: Concepts, Methodologies, and Tools》, D.Clein, Newnes, 1999.

[3]《The StrongARM Latch》(A Circuit for all seasons), B.Razavi, IEEE Solid-State Circuits Magazine, v. 7, no.2, p. 12-17, 2015.