-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

-

產品系列

查看所有產品Ansys致力於為當今的學生打下成功的基礎,通過向學生提供免費的模擬工程軟體。

-

ASIC 設計流程:ASIC 設計是什麼?

什麼是 ASIC?

ASIC 是特定應用的積體電路,這是精心設計的特殊類型積體電路,可在電子系統中執行特定功能或一組功能。不同於一般用途的微處理器,如您的微波爐或電視盒等日常電子裝置所使用的,ASIC 是專為特定應用量身打造,提供無與倫比的效率與效能。

ASIC 包含多種不同的電子產品,能將外部電路需求降至最低。由於 ASIC 開發是專為特定應用量身打造的定製性質,因此可能會有較高的成本。然而,當設計用於大量產品時,這種支出可以被合理化甚至被視為具成本效益性。

ASIC 設計的類型

ASIC 設計的主要方法有兩種:

- 閘陣列 (半定製設計)

- 全定製設計

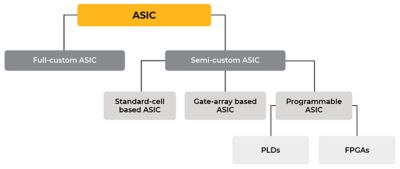

半定製設計分為幾個組別。ASIC 的分類顯示如下:

ASIC 類型

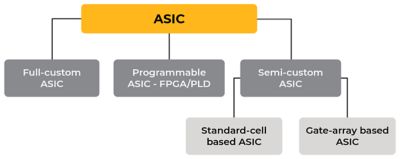

有時會將可程式化的 ASIC 視為與半定製 ASIC 不同。其他 ASIC 分類的顯示如下:

ASIC 分類

全定製設計:全定製方法比較複雜且成本高昂,但是它的功能遠遠超過閘陣列方法。ASIC 的大小會大幅縮減,因為設計中僅包含必要的閘和電子元件,會刪除未使用的閘。這些 ASIC 是專為特定用途所設計,支援最終產品中的特定功能。

半定製 ASIC:此方法包含預先定義擴散層,電晶體及其他主動式裝置,讓初始設計的工作量降至最低,藉此降低非經常性的工程成本。 由於使用金屬鍍層程序,因此生產週期會大幅縮短,相較於全定製設計,這是相對快速的程序。在最後的設計階段,工程師會操縱特定的開關,根據所需的規格開啟與關閉這些開關,來引導晶片的行為。

標準元件型 ASIC:此類型的 ASIC 使用稱為標準元件的預先設計邏輯元件,例如,閘、多工器和正反器。標準元件是以全定製的設計方法製造,並作為 ASIC 設計的基本建構模塊,確保擁有相同的效能與彈性,同時減少時間與風險。

邏輯閘陣列型 ASIC:這種類別的 ASIC 中,電晶體,邏輯閘和其他主動式裝置是以矽晶圓建立與製造,而在製造期間並未形成互連。閘陣列上預先建立的電晶體配置稱為基座陣列,而形成閘陣列的最小重複元件稱為基座元件。此方法有多項優點,包括周轉時間縮短,邏輯密度更高,以及定製化的接觸層。

可程式化 ASIC:此類型的 ASIC 可在製造後在硬體層進行程式設定。與專為特定應用量身打造的傳統 ASIC 不同,可程式化的 ASIC 可提供您所需的彈性並進行重新程式化。可程式化邏輯裝置 (PLD) 和現場可程式化閘陣列 (FPGA) 是可程式化 ASIC 的完美範例。

ASIC 的應用

ASIC 可在不同產業中發揮應用,每個應用均可以獨特用途運用技術。以下是 ASIC 扮演關鍵要角的幾個重大產業:

消費性電子元件:許多消費性電子產品中都有 ASIC,驅動著智慧型手機,數位相機和智慧型電視等裝置。其能提供量身打造的解決方案,強化了這些小工具的整體效能和電源效率。

電信:網路設備,路由器和通訊裝置中會用到 ASIC。其定製設計的特性可確保處理資料的功能和速度達到最佳化。

汽車產業:ASIC 可為汽車產業提供顯著的貢獻,並將其整合至各種系統,例如引擎控制單元 (ECU),先進駕駛輔助系統 (ADAS),以及資訊娛樂系統。

醫療保健:醫療裝置,診斷設備和影像系統通常會採用 ASIC,以達到精密,可靠及電源效率的嚴格要求。

ASIC 設計流程

ASIC 的設計是包含數個階段的縝密流程,每個階段都對打造高度專業化的晶片不可或缺。ASIC 設計的關鍵階段包括:

規格與需求:這是 ASIC 設計流程的第一階段,該流程包含定義開始設計程序的規格與需求。其中包含收集相關利害關係人的意見,並將重點產品規格轉化為詳細的技術規格。必須明確列出預期的輸出、效能目標,耗電量目標及其他重要參數。

架構設計:規格有了後,就會設計 ASIC 的架構。這包括確定整體結構,功能區塊的配置,以及這些區塊之間的互連。工程師必須集思廣益找出各種可能的想法,並仔細考量效能影響、技術可行性和硬體資源,從中選擇理想的方法,並同時將整體成本維持在指定的預算範圍內。

RTL 設計:暫存器傳輸級 (RTL) 設計涉及使用硬體描述語言 (HDL) 說明 ASIC 的功能。此階段是抽象架構設計與實體實作之間的橋樑。

驗證:驗證可透過在測試平台上測試和模擬設計,確保 ASIC 符合指定的要求。這個階段對於辨識及修正任何設計瑕疵或問題至關重要。

合成與實作: 在合成期間,會將 RTL 代碼轉換為閘等級網表,代表 ASIC 的實體實作。此網表會轉譯成佈局,而實體設計則針對耗電量,速度和區域最佳化。

簽核與下線:完成實體佈局後,下一步是根據晶圓廠建議的設計規則來確認實體設計。工程師會執行電路佈局驗證 (LVS) 檢查與設計規則檢查,這會使用模擬工具視需要修改設計。此流程稱為「簽核」。一旦設計通過指定的設計規則,就會下線送到晶圓廠進行製造。

製造:最後一個步驟是使用半導體製程製造 ASIC。這個步驟需要與有能力生產定製設計的晶片的半導體晶圓廠合作。選擇正確的晶圓廠,有助於達到所需的成果。

ASIC 的優點

效能最佳化:ASIC 是專為特定工作發揮卓越效能而設計,僅為其特定功能具備重要的電路。其精簡化設計提供無可比擬的效能與效率,超越一般用途處理器,具備小巧尺寸與較低的耗電量。

電源效率:ASIC 因為是定製的,所以可減少不必要的元件,進而改善電源效率並降低能源消耗。

空間最佳化:ASIC 可依特定外型規格量身打造,讓電子裝置更能節省空間。

以量達到成本效益:雖然 ASIC 設計與製造的初始成本可能很高,但由於沒有冗餘組件,因此在大量製造時,成本效益會大幅提高。

提升效能與效率一直是電子產業的優先要務。ASIC 特定應用的性質對整個業界帶來的影響顯而易見,不但推動創新,更提升電子裝置的功能。為了讓 ASIC 的設計程序更有效率、快速且更具成本效益,需要審慎選擇設計和模擬軟體。隨著不斷提升的速度和縮減的尺寸,設計師必須超越傳統技術,並解決新興的多物理挑戰。

在此深入了解多物理模擬的重要性:Ansys 半導體解決方案

相關資源

讓我們開始吧

如果您面臨工程挑戰,我們的團隊將隨時為您提供協助。憑藉豐富的經驗和對創新的承諾,我們邀請您與我們聯絡。讓我們共同合作,將您的工程障礙轉化為成長和成功的機會。立即與我們聯絡,開始對話。