-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

-

產品系列

查看所有產品Ansys致力於為當今的學生打下成功的基礎,通過向學生提供免費的模擬工程軟體。

-

動態電壓降分析是一個複雜的過程。若要成功執行適當的分析,必須結合多個輸入檔案和不同的組態設定。

切換情境是任何動態電壓降分析的關鍵。設計中的所有閘和實例將不會同時處於活動狀態。此外,對於更複雜的單元,可能的切換模式會很多。這些實例切換的確切時間也可能有所不同。同一位置附近的許多實例同時切換或按順序關閉,可能會導致局部電壓降熱點。切換情境是指每個實例中隨著時間發生的資料切換。動態分析的好壞取決於切換情境的品質。如果切換情境可以在更短的模擬時間內發現更多電壓降違規事件,則工程師可以更輕鬆地改善電網的穩健性。

要建立此切換情境有不同的方法。明顯的方法是依賴在其他地方進行功能模擬所建立的資料。這可以透過向量檔案提供。雖然 VCD (值變更轉儲) 和 FSDB (快速訊號資料庫) 都是可用的檔案格式,而 FSDB 是最常見的格式,但我們會使用 VCD 這個術語來指涉這兩種向量檔案。使用 VCD 是一種簡單且直接的方法,導入切換情境資訊以進行動態分析。

然而,使用 VCD 輸入來進行電壓降分析會面臨許多限制。首先,取得 VCD 是一項挑戰,因為全面的功能模擬只會在設計週期的尾聲完成。電壓降分析則無法等那麼久才開始。此外,VCD 僅適用於部分功能模式,對於電壓降分析來說可能不是最適合的。

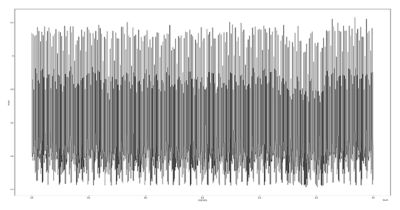

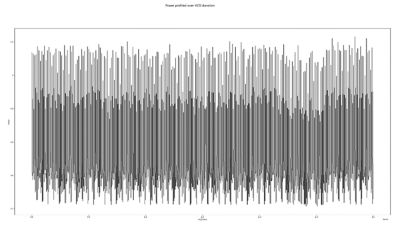

在長時間值變更轉儲 (VCD) 期間進行功率剖析

大多數工程師進行電源完整性分析都傾向於使用無向量方法來建立切換情境,而這種方法是由軟體完成分析的。這些無向量方法在設定方面提供了很大的靈活性,並提供了更好的切換覆蓋範圍。這種方法的缺點是,無向量切換情境不是實際的功能模式。

這就是暫存器傳輸級 (RTL) VCD 派上用場之處。這些是前端設計驗證端提供的 VCD。與閘極或網表層級 VCD 相比,RTL VCD 在設計週期的早期即可使用,比功能模式的持續時間長得多,而且更易於取得。

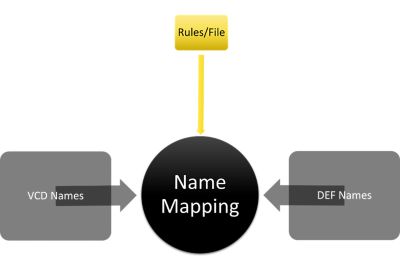

軟體本身可以緩解將 RTL VCD 導入電源完整性分析的兩個關鍵挑戰。其中一個挑戰是,VCD 實際上源自設計的 RTL 階段,因此在合成過程中名稱會有所變更。必須在 RTL VCD 中的訊號與網表或設計交換格式 (DEF) 中的引腳或信號線之間進行適當的名稱對應。這是透過進行智慧型名稱對應來解決,其中會研究合成期間的字串模式和常見命名變更,並將其編碼至電源完整性軟體中。使用者也可以從合成或正式驗證階段取得資料,並將其放入名稱對應檔案中。

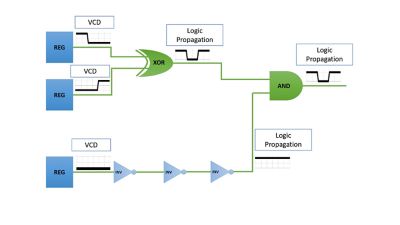

第二個挑戰是,事件或切換模式僅適用於設計中的時序元件,但它們需要在整個設計中傳播 (例如組合邏輯和時脈樹網路)。這也可在電壓降分析軟體中完成。這些可以推斷單元功能,並將事件從觸發器傳遞到組合邏輯。事件的確切時間可以從延遲傳遞或使用靜態時序分析 (STA) 檔案輸入來得出,每個實例都有抵達時間。

VCD 名稱對應

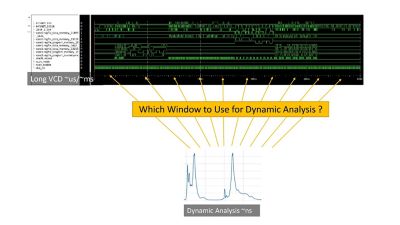

下一個挑戰不限於 RTL VCD。在任何輸入 VCD 的情況下,都會面臨從 VCD 持續時間內選擇一個小窗口來進行動態電壓降分析的挑戰。VCD,無論是閘極還是 RTL,都可能很長:微秒甚至到毫秒。也可能有不只一個 VCD。然而,暫態電源完整性分析最好在更短的持續時間內進行,例如在奈秒範圍內。因此,需要選擇 VCD 窗口。

使用者通常會採用某種形式的 VCD 剖析。最受歡迎的方法是使用 VCD 窗口,因為它具有最高的功率。高功率大多等同於高電流,而高電流預期會發現大多數的電壓降違規問題。此剖析階段會貫穿整個 VCD 持續期間,並在橫跨 VCD 的短間隔內找出功率。然後,這些資料會用來找出功率最高的窗口。還有其他進階方法,例如尋找功率變化最大的 VCD 窗口,查看區域範圍的功率數字,或結合使用上述方法。使用者也可導入阻抗和時序窗口重疊資料,以更好地最佳化 VCD 窗口選擇程序。根據時間和資源可用性,工程師還可以選擇橫跨多個 VCD 窗口進行電壓降分析。

VCD 功率剖析

Ansys 半導體晶片設計解決方案,包括適用於數位和 3D 積體電路 (3D-IC) 的 Ansys RedHawk-SC 電源完整性簽核平台,已被世界上許多頂尖公司廣泛採用超過 10 年之久。RedHawk-SC 軟體已為無數設計在 RTL 和閘極之間對應名稱,服務眾多客戶和技術世代。此平台透過新增智慧和設定/調節器而持續追求進步,以提升對應效率。因此,RedHawk-SC 軟體具有非常健全的名稱對應機制。

同樣地,RedHawk-SC 軟體廣泛處理先進設計,以及它克服高品質挑戰,使其對事件傳遞特別有效。還有一個流程可確保設計時脈網路中反映的邏輯事件準確無誤。由於大多數整合式時脈閘 (ICG) 都會插入到設計的後合成中,因此 RTL VCD 中不會擷取這些內容。透過在時序實例中傳遞來自 VCD 事件的訊號,RedHawk-SC 軟體可以推斷邏輯訊號發生在這些 ICG 的啟動引腳上。然後這會用來成為這些 ICG 的閘極。因此 ICG 及其下游時脈網路將有對應 RTL VCD 輸入的事件。

RedHawk-SC 軟體建立在 Ansys SeaScape 雲端最佳化並適用於電子設計自動化的大數據分析平台之上。這將大數據分析引入半導體設計分析領域。除了支援分散式運算處理之外,SeaScape 平台還能讓使用者定義處理資料的新方法,並提出可操作的結果。這是 VCD 窗口選擇的未來,在這種情況下,可以結合更多資料和功率剖析中的資訊,以實現更多最佳分析流程。

RTL VCD 為選擇正確切換情境以進行動態電壓降分析的複雜層面提供了有效的解決方案。啟用此流程的挑戰包括 VCD 名稱對應、事件傳遞和向量窗口選擇。RedHawk-SC 軟體具有強大的 VCD 名稱對應流程和執行邏輯事件傳遞的原生解決方案,以及高效的功率剖析流程,可透過其他資料點的輸入輕鬆擴充。

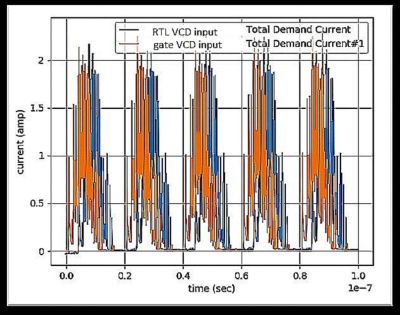

比較具備邏輯事件傳遞的暫存器傳輸級 (RTL) VCD 輸入的需求電流,和具有同等閘極 VCD 輸入的執行的需求電流

邏輯事件從暫存器的 VCD 訊號傳遞到設計的其餘部分

深入瞭解 RedHawk-SC 軟體和 Ansys 的其他半導體設計解決方案。