-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

-

產品系列

查看所有產品Ansys致力於為當今的學生打下成功的基礎,通過向學生提供免費的模擬工程軟體。

-

ANSYS 部落格

July 19, 2023

減輕晶片設計中的電遷移 (Electromigration)

從智慧型手機到筆記型電腦,我們每天都會使用各種仰賴積體電路 (IC) 或晶片才能運作的裝置。這些晶片是由數千個電晶體和互連組成,會從晶片的某一部分將電子訊號傳送至另一個部分。然而,為了速度和複雜度的需求,必須讓更多能源流經更小的裝置,這種集中的電流流動可能會透過「電遷移」的現象,對晶片效能造成威脅。

什麼是電遷移?

電遷移是電流流動導致的原子移動。

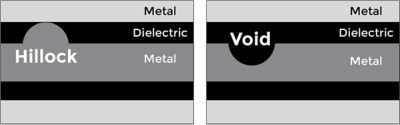

這種移動會改變導體的實體結構,因為其會形成空孔或凸起,而這可能導致短路、開路、效能下降或裝置故障。由於通過互連的電流密度增加,因此電遷移率也隨之增加,使得電遷移成為失控的程序。事實上,電遷移是造成電路故障的主要原因。

圖片顯示由於金屬原子遠離部分區域,移往其他區域,因此發生電遷移,進而在半導體互連中形成空孔和凸起的情況

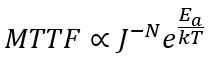

電遷移程序的速度可能會因電流較高、溫度較高、機械壓力提升、導體缺陷及存在雜質等因素而加快。這可透過 Black 方程式計算而得,這種 Arrhenius 方程式以經驗為依據,可透過平均故障間隔時間 (MTTF) 來說明此現象:

- J:電流密度

- N:比例因數

- k:Boltzmann 的常數

- T:溫度 (以 K 為單位)

- Ea:啟動能量 (以 J 為單位)

Black 方程式是由 Robert Black 在 1969 年推導所得,可計算電遷移會對設計造成什麼影響,協助工程師瞭解電路的潛在使用壽命。此方程式在 MTTF 以及電線的電流密度、溫度和材料特性之間建立了關聯。

電流密度:由於較粗的電線具有較大的截面面積,因此電流密度較低,較不易受到電遷移影響。

溫度:隨著溫度升高,原子的移動速度會加快,提高電遷移的可能性。

材料特性:部分材料對電遷移具有較大的抗性。例如,銅具有高導電度,因此成為比鋁更受歡迎的選擇。

隨著電子裝置的小型化程度越來越高,電遷移的可能性及其造成的問題也大幅增加。由於晶片有責任讓這些裝置保有可靠效能,因此必須減輕電遷移以維持產品的功能性。

如何在晶片設計中減輕電遷移的影響

為了避免電子元件中金屬移轉失敗或造成危險,晶片設計師可以使用數種技巧,包括:

- 增加互連寬度以降低電流密度。

- 使用對電遷移具有高抗性的材料,例如黃金與銅。

- 使用冗餘孔位讓電流強度轉向。

- 縮減互連之間的間隔。

- 針對較低電壓位準設計電路。

當然,若要在晶片設計中解決電遷移,可能需要混合運用多項技巧。為超大規模整合 (VLSI) 設計互連時,模擬軟體可協助針對特定電流需求判斷出最佳選項。晶片設計師必須分析通過互連的電流密度,以及電阻提高的各項原因來預測晶片中的電遷移。

互連長度增加以及寬度縮減、高電流密度和散熱不良等,都需要採用極度複雜的電磁原則,才能在進階技術節點中處理這些挑戰。

晶片設計中的電遷移測試與監控

為了在晶片設計中實現可靠性,工程師必須在許多不同設計選擇之間權衡取捨。例如,增加互連寬度會降低電阻和電流密度,並增加電容。或是選擇縮減互連之間的間隔,能幫助進行整合,但也會增加串擾耦合。

Ansys RedHawk-SC 等模擬軟體可讓晶片設計師預測並分析互連的行為,於是可在晶片進入製造階段前,先決定如何在系統內分配功率。使用模擬技術來測試、驗證和監控晶片設計,不僅可改善電子效能,也能協助公司避免成本高昂的錯誤和必須召回產品。

結果:可靠的電子產品

電遷移是晶片設計與製造中的關鍵問題。雖然電遷移可能造成破壞性的影響,但仍可採取數項措施來預防或將其影響降至最低。藉由將互連設計最佳化、選擇正確的材料、控制溫度,以及謹慎管理製程,即可降低電遷移的風險。

隨著電子產品不斷進步,瞭解並解決電遷移帶來的挑戰至關重要,如此才可確保晶片的可靠性和使用壽命。使用 Ansys Redhawk-SC 和 Ansys Totem 等進階模擬簽核工具,工程師可以打造更快速、更強大且更可靠的系統,即使在最狹窄的空間內也能做到。