-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

-

產品系列

查看所有產品Ansys致力於為當今的學生打下成功的基礎,通過向學生提供免費的模擬工程軟體。

-

ANSYS BLOG

June 2, 2022

IR-ECO: Is it Possible to Fix Voltage-Drop Violations Without Destroying Your Chip Timing?

Experience has taught chip designers that it is very difficult to correct voltage drop (IR drop) issues late in the design process. IR-ECO (engineering change orders) are especially difficult because competitive pressures always push chip performance to the absolute limit and design changes intended to fix IR drop end up damaging timing, which leads to more edits and unintended consequences. The upshot is that designers in the past felt it necessary to over-design the power distribution network to avoid having any IR drop issues crop up later.

But over-design is no longer a viable option with today’s advanced silicon processes for three reasons.

1. The extreme pressure to reduce power consumption has led to lowered supply voltages, sometimes to just over half a volt. This means that voltage margins have become razor thin and the amount of over-design that would be required to eliminate it is prohibitive.

2. The relative impact of dynamic voltage drop (DVD) has increased dramatically. Strong local current surges caused by the simultaneous switching of neighboring cells can cause significant transient voltage drops that are difficult to predict, given the astronomical number of possible switching scenarios.

3. The switching speed of tiny nanometer-scale logic gates are now very sensitive to the supply voltage. Because of this, even small IR dips will slow the signal path through that gate. This effect is at its worst for critical timing paths that already have no timing slack to spare.

Designers are thus left in the difficult situation of discovering a number of unexpected DVD-induced voltage issues and timing failures as they approach timing closure. In the past, these were fewer in number and IR-ECO could be resolved with some manual intervention. Today, designs are bigger, frequencies are higher, and IR drop issues have quickly become too numerous and interconnected for manual interventions. There is a need for better fixing guidance and root-cause analysis to help designers efficiently fix IR problems in a way that absolutely minimizes the number of changes they need to make.

Technology, Timing and Voltage Drop

A technology solution is needed to resolve the deep interdependence between timing and voltage drop. Voltage drop analysis and static timing analysis have usually been very distinct operations with no coordination. However, any attempt to speed up a path usually involves the addition of higher drive strength gates, which draw more power and, hence, more DVD. Alternatively, path elements can be placed closer together to reduce interconnect delay, but this means that the effect of any local DVD impacts multiple gates on the same critical path, amplifying the timing impact. Traditional electronic design automation (EDA) flows are not able to resolve this interdependence without considerable manual intervention.

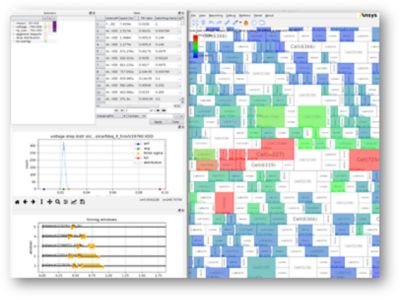

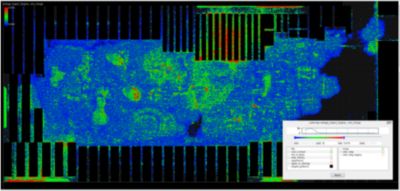

Ansys RedHawk-SC provides a highly interactive graphical debugging environment that shows root-causes for dynamic voltage drop.

An example of a graphical display by Ansys RedHawk-SC showing which cells are most affected by dynamic voltage drop.

An obvious solution to voltage/timing interdependence would be to simply check the DVD impact of any timing ECOs before accepting a change. Unfortunately, DVD analysis requires running multiple activity vectors through the entire modified design, which is computationally expensive and makes this solution time prohibitive.

IR-ECO has clearly grown to become a major impediment to quick and efficient timing signoff, requiring multiple iterations with manual edits to resolve. Ansys has been leading the industry with innovations in voltage drop analysis and open platform approach to multi-vendor integration.

Learn more about Ansys RedHawk-SC, the industry leader in voltage drop multiphysics signoff software.