-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

-

產品系列

查看所有產品Ansys致力於為當今的學生打下成功的基礎,通過向學生提供免費的模擬工程軟體。

-

ANSYS BLOG

June 8, 2020

How to Design Foundry-Compatible Custom Photonic Components

The next episode of Ansys’ photonics webinar series is set to unveil the latest Lumerical photonics simulation-based design flow to build custom components. Ansys is a driving force in the emerging photonics ecosystem as it works with foundry partners to offer workflows that reduce development cycles and improve manufacturability.

The demand for photonics technology is growing with popular applications such as datacom (5G), artificial intelligence (AI), sensing, quantum computing and autonomous driving. The improved bandwidth, sensing capabilities and reduced power consumption of photonics is making this growth possible.

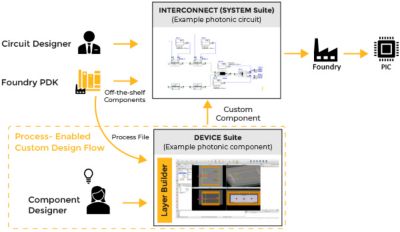

To help photonics design engineers, Ansys Lumerical’s SYSTEM Suite is used in a process design kit (PDK)-driven flow that is familiar to the electronics industry. Armed with a library of manufacturing-ready, off-the-shelf components within a PDK, designers can easily build photonic integrated circuits (PICs) that adhere to foundry processes.

A foundry process file that is packaged with the PDK contains all the information necessary for Ansys Lumerical’s DEVICE Suite to simulate components that can be manufactured using the foundry process.

As a result of Ansys’ close collaboration with its foundry partners, two leading silicon photonics foundries, CompoundTek and Tower Semiconductor, now provide process files compatible with Ansys Lumerical tools.

How Custom Components Become Reality with the Process-Enabled Custom Design Flow

The process-enabled custom flow utilizes process files for foundry-accurate simulations in Ansys Lumerical FDTD, the finite-difference simulation tool available with Ansys Lumerical’s DEVICE Suite.

The process file makes it easier for engineers to simulate custom components accurately for a specific foundry process. The process-enabled flow significantly improves the likelihood of successful fabrication, saving the time and cost of numerous re-fabrications.

Layer Builder is a key feature of the process-enabled custom design flow in Ansys Lumerical’s DEVICE Suite. The Layer Builder generates a 3D model from a design layout (typically in GDS format) provided by the component designer and a process file provided by the foundry.

The process file contains critical information that is typically found in technology handbooks from the foundry (including the vertical position, thickness, material and sidewall angle of each process layer). Without a process file, it is necessary to manually configure the CAD model, which is a cumbersome, time-consuming and error prone step. By using a process file verified by the foundry, component designers spend less time configuring the geometry of their simulation and more time focusing on design and optimization efforts.

The Layer Builder can be fully accessed and configured using Ansys Lumerical's scripting language. Combined with Ansys Lumerical’s Automation API, Layer Builder enables highly customized flows for component design.