-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

-

產品系列

查看所有產品Ansys致力於為當今的學生打下成功的基礎,通過向學生提供免費的模擬工程軟體。

-

Ansys Blog

November 16, 2020

5 Ways to Improve Photonics Manufacturing Outcomes

Popular applications such as datacom (5G), artificial intelligence (AI), sensing, quantum computing and autonomous vehicles are driving demand for photonics technology. Photonics benefits these applications through improved bandwidth, easier miniaturization, better sensing capabilities and reduced power consumption.

However, photonics design and manufacturing are challenging for startups and well-established foundries and design houses alike. As discussed in the next episode of Ansys’ photonics webinar series, a well-defined workflow centered around statistically enabled compact models is key.

Below are five ways to improve photonics manufacturing outcomes.

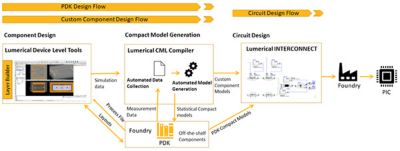

1. Improve Productivity with Automated Compact Model Creation

One of the most challenging aspects of photonics process development kits (PDKs) is delivering accurate compact model libraries for system simulation. Generating and maintaining compact models is time-consuming, cumbersome and error prone because they encompass a wide variety of data types and models. To date, data formats and exchange mechanisms have been ad hoc, resulting in varying levels of quality and lengthy development cycles.

You can improve productivity by automating the creation of compact models. Ansys’ Lumerical CML Compiler is a trusted tool for automatically generating compact models that leverages built-in photonics expertise for consistent, high-quality results.

2. Improve Simulation Accuracy with Yield Analysis

You can extend simulation performance to account for real-world variability through yield analysis with statistical compact models. By capturing variability inherent to the fabrication process, simulation results better capture the true behavior of the circuit after fabrication. Process variability has a significant impact on the performance of photonic integrated circuits and includes statistical correlations of individual circuit elements in addition to spatially dependent variability. Yield analysis leads to circuits that are more likely to work correctly the first time, resulting in faster time to market, reduced fabrication costs and a better return on investment.

Ansys Lumerical CML Compiler can generate statistically enabled compact libraries. These can be loaded into Ansys’ photonic circuit-level simulation tool Lumerical INTERCONNECT, to perform yield, Monte Carlo analysis and corner analyses.

The use of automated model generation statistical data and process files in

component-level and system-level designs flows results in improved

manufacturing outcomes.

3. Build Custom Components with Foundry Process Files

You can simulate custom components with confidence using foundry process files that ensure results that accurately match the specific foundry process. The process file contains critical information typically found in technology handbooks from the foundry (including vertical position, thickness, material and sidewall angle of each process layer). Using a process file eliminates the need to manually configure the computer-aided design (CAD) model, a cumbersome, time-consuming and error prone step. By using a process file verified by the foundry, you can spend less of your time configuring the geometry of your simulation and more time focusing on design and optimization efforts.

With only your graphic design system (GDS) and process file, you can go directly to simulation with Ansys’ process-enabled custom design flow. Available for Ansys’ Lumerical component level tools, the flow significantly improves the likelihood of successful fabrication, saving the time and cost of numerous re-fabrications. A key feature of the flow is the Layer Builder that generates a 3D model from a design layout (typically in GDS format) provided by the component designer and a process file provided by the foundry.

4. Automatically Calibrate Models with Measured and Simulated Data

Though important, compact model calibration is time consuming, cumbersome and error prone. Automating model calibration saves you time and ensures your compact models are consistent and accurate. It enforces physical behavior and self-consistency when combining data from different sources.

Ansys Lumerical offers automated workflows that supplement measured data with automatic simulation. It provides input to CML Compiler, and it includes a broad set of valuable data visualization features and diagnostics.

5. Explore Ansys’ Photonics Ecosystem Partners

Explore a variety of workflows developed with Ansys’ Lumerical ecosystem partners, including foundries and electronic design automation (EDA) tool providers, to meet the needs of your application. Leverage advanced flows and interoperability to improve productivity, reduce risk and meet your aggressive deadlines.

For a detailed description of Ansys’ statistically enabled workflow for compact models that leverages these concepts, please join us for the webinar: Building and Using Statistical Compact Models for Circuit Level Yield Analysis.