-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

Ansys는 학생들에게 시뮬레이션 엔지니어링 소프트웨어를 무료로 제공함으로써 오늘날의 학생들의 성장을 지속적으로 지원하고 있습니다.

-

Ansys는 학생들에게 시뮬레이션 엔지니어링 소프트웨어를 무료로 제공함으로써 오늘날의 학생들의 성장을 지속적으로 지원하고 있습니다.

-

Ansys는 학생들에게 시뮬레이션 엔지니어링 소프트웨어를 무료로 제공함으로써 오늘날의 학생들의 성장을 지속적으로 지원하고 있습니다.

ANSYS 블로그

May 3, 2023

3D-IC 설계: 칩 통합을 위한 혁신적인 접근 방식

기술의 발전으로 인해 점점 더 복잡해지고 밀도가 높아지는 집적 회로(IC)가 개발되었습니다. 고성능 및 전력 효율이 높은 장치에 대한 수요가 증가함에 따라, 업계는 3D-IC 설계로 전환했습니다. 3D-IC는 가전제품, 통신, 컴퓨팅, 자동차 등 광범위한 산업에서 다양한 분야에서 응용되고 있습니다.

3D-IC 기술이란 무엇입니까?

3D-IC 기술은 멀티 다이 집적 회로를 위한 다양한 패키징 기술을 의미하며, "칩렛(chiplet)"이라고 불리는 다수의 반도체 칩이 서로 가깝게 배치되거나(2.5D-IC),층층이 적층되는(3D-IC) 기술을 말합니다.. 칩렛은 실리콘 인터포저와 TSV(Through Silicon Via)를 사용하여 상호 연결되며, 이는 실리콘 인터포저를 통해 침투하여 모든 레이어 간에 연결을 가능하게 합니다 TSV는 더 짧은 연결 길이, 더 낮은 기생 용량, 더 높은 대역폭을 제공하여 시스템 성능을 향상시킵니다. 이 기술을 사용하면 논리, 메모리, 센서, MEMS(Micro Electro Mechanical System) 등과 같은 이질적인 칩의 통합을 가능하게 하여, 높은 성능,낮은 전력 소비 및 소형화를 가능하게 합니다.

3D-IC 기술이 더 나은 대안인 이유는 무엇입니까?

SOC(System-on-Chip)는 더 높은 성능과 확장된 기능을 제공하므로 모든 IC 설계자가 가장 먼저 선택하는 솔루션입니다. 그러나 SOC는 모놀리식이며, 혼합 요소를 단일 다이로 통합하면 제품 전달이 지연되고 IC의 전체 비용을 증가시킵니다.

SOC 설계 방법에는 몇 가지 제한 사항이 있습니다. 주요 제한 사항 중 하나는 전자 시스템의 모든 구성 요소가 단일 칩에 배치되기 때문에 칩 자체의 크기입니다. 이는 SOC에 통합할 수 있는 구성요소의 수와 유형이 칩의 사용 가능한 공간에 의해 제한된다는 의미입니다.

SOC 설계의 또 다른 한계는 제조 공정의 비용과 복잡성입니다. 단일 칩에 많은 부품이 집적되어 있기 때문에 고급 반도체 제조 공정이 필요하며 이는 비용이 많이 들고 복잡할 수 있습니다. 이로 인해 SOC를 대량으로 생산하는 것이 어려워지고 상업적 실현 가능성을 제한할 수 있습니다.

모든 구성 요소가 SOC 패키지에 촘촘하게 포장되어 있기 때문에 전력 소비가 증가하고 성능이 저하됩니다. 높은 수준의 통합은 또한 시스템의 유연성과 업그레이드 가능성을 제한합니다. 전반적으로 SOC 설계는 더 작은 크기와 복잡성 감소 등 많은 이점을 제공하지만 이 접근 방식을 사용하기로 결정하기 전에 잠재적인 제한 사항을 신중하게 고려하는 것이 중요합니다.

위에서 언급한 제한 사항으로 인해 설계자는 더욱 혁신적인 접근 방식인 3D-IC 설계를 채택하도록 장려했습니다. 이 접근 방식은 성능 향상, 전력 소비 감소, 폼 팩터 소형화 등 기존 2D-IC 설계에 비해 여러 가지 이점을 제공합니다. 3D-IC 설계 기술을 통해 기존 2D-IC 대비 이기종 집적화, 공간 활용 효율화, 전기적 성능 향상 등이 가능합니다.

3D-IC는 서로 다른 IP 간의 더 나은 연결을 위해 실리콘 인터포저와 TSV를 사용합니다. 실리콘 인터포저는 단일 패키지에서 여러 다이 또는 칩을 연결하기 위해 2.5D 및 3D-IC 설계에 사용되는 얇은 실리콘 웨이퍼입니다. 이는 미세 간격 수직 TSV 및 마이크로범프를 사용하여 다이를 배치하고 연결하는 기판 역할을 합니다. 이를 통해 기존 2D-IC에 비해 더 나은 방열, 전력 소비 감소, 더 높은 밀도 및 향상된 전기적 성능을 제공합니다

3D-IC의 설계 과제

3D-IC 설계에는 열 전달, 일렉트로마이그레이션, 응력 및 변형, 열팽창 등 여러 가지 다중물리 과제가 있습니다. 이러한 과제는 여러 개의 다이가 서로 적층되고 TSV 및 마이크로범프를 사용하여 연결되는 3D-IC의 복잡하고 상호 연결된 특성으로 인해 발생합니다.

열 팽창도 3D-IC 설계에서 어려운 과제입니다. IC의 온도가 변함에 따라 IC에 사용되는 다양한 재료가 다양한 속도로 팽창하여 성능과 신뢰성에 영향을 미칠 수 있는 응력과 뒤틀림을 유발합니다. 열 전달은 3D-IC 설계의 온도 분포를 더욱 복잡하게 만들 수 있습니다. 트랜지스터 및 기타 부품의 밀도가 높기 때문에 3D-IC에서는 열 전달이 어렵습니다. 대부분의 열은 시스템에 갇히게 되어 온도가 상승하게 됩니다. 이러한 현상을 self heating이라고 합니다. 3D-IC는 긴 상호 연결 와이어를 통해 연결된 수십억 개의 구성 요소로 구성됩니다. 이러한 긴 연결로 인한 줄 가열은 전체 온도 상승에 기여하는 또 다른 주요 문제 영역입니다. 안정적인 성능을 보장하려면 3D-IC를 설계할 때 이러한 열원을 모니터링하고 분석해야 합니다.

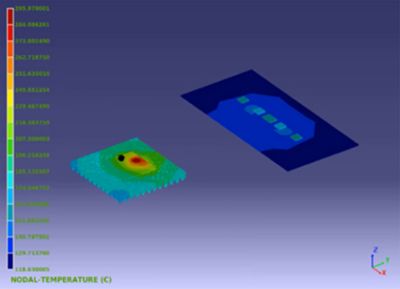

멀티 다이 3D-IC 시스템의 열 분포

Ansys RedHawk-SC Electrothermal은 실리콘 인터포저를 사용하여 3D-IC 설계의 열 동작을 검사하고 시뮬레이션하는 표준 기술을 제공합니다. 실리콘 인터포저를 포함하여 3D-IC 설계의 형상 및 재료 특성을 쉽게 모델링하고 설계 내 열 전달을 시뮬레이션할 수 있습니다. 또한 온도 분포와 열 방출을 쉽게 분석하여 설계가 필요한 열 성능 사양을 충족하는지 확인할 수 있습니다.

일렉트로마이그레이션은 3D-IC 설계의 또 다른 주요 과제입니다. 이것은 도체 내 전자의 이동을 의미하며, 이는 시간이 지남에 따라 IC에 손상을 줄 수 있습니다. 이는 높은 전류와 부품 밀도로 인해 3D-IC에서 특히 문제가 되며, 이는 일렉트로마이그레이션의 위험을 증가시킬 수 있습니다. 엔지니어는 Ansys Redhawk-SC를 사용하여 두 번 생각할 필요 없이 일렉트로마이그레이션 신뢰성을 승인할 수 있습니다.

전력 무결성과 신호 무결성은 항상 모든 IC 설계자의 최우선 관심사입니다. 3D-IC에서는 복잡한 기하학적 구조로 인해 전력 무결성 사인오프가 더 복잡합니다. 전력과 온도 사이의 관계는 이를 더욱 복잡하게 만듭니다. 시스템의 각 블록의 전력 소비량이 다르므로 각 블록 주위에 서로 다른 온도 분포가 생성됩니다. 시스템의 전력 무결성을 최적화하려면 설계자는 3D-IC에 존재하는 이러한 다중물리 문제를 극복해야 합니다. Ansys 소프트웨어를 사용하면 블록에 대한 전력 모델을 쉽게 생성하고 시스템 동작을 시뮬레이션할 수 있습니다.

3D-IC 설계는 작은 폼 팩터를 제공하지만 다중물리 과제가 많은 칩 통합에 대한 혁신적인 접근 방식입니다. 성공적인 설계 및 구현을 위해서는 이러한 다중물리 과제를 해결하는 것이 중요합니다. Ansys 도구는 동급 최고의 시뮬레이션 기술을 제공하여 문제를 쉽게 해결할 수 있는 기능을 갖추고 있습니다. 3D-IC의 신호 무결성, 전력 무결성 및 열 무결성을 쉽게 분석하여 설계가 필요한 모든 성능 사양을 충족하는지 확인할 수 있습니다.

RedHawk-SC에 대해 알아보고 관련 웨비나 "실리콘 인터포저 설계의 열 무결성 과제 및 솔루션"을 확인하십시오.