기본 사양

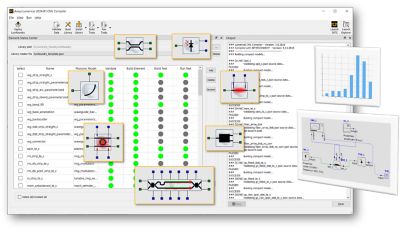

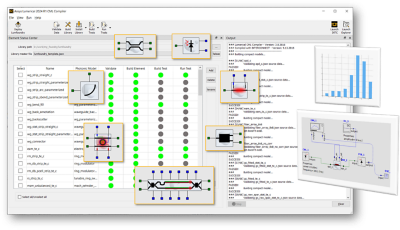

Lumerical CML Compiler는 측정 또는 시뮬레이션 데이터의 단일 소스에서 고품질 INTERCONNECT 및 포토닉 Verilog-A 컴팩트 모델을 구축할 수 있는 효율적인 방법을 제공합니다.

Ansys는 학생들에게 시뮬레이션 엔지니어링 소프트웨어를 무료로 제공함으로써 오늘날의 학생들의 성장을 지속적으로 지원하고 있습니다.

Ansys는 학생들에게 시뮬레이션 엔지니어링 소프트웨어를 무료로 제공함으로써 오늘날의 학생들의 성장을 지속적으로 지원하고 있습니다.

Ansys는 학생들에게 시뮬레이션 엔지니어링 소프트웨어를 무료로 제공함으로써 오늘날의 학생들의 성장을 지속적으로 지원하고 있습니다.

안심할 수 있는 CML 구축 및 유지 관리

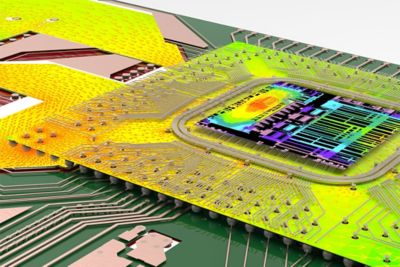

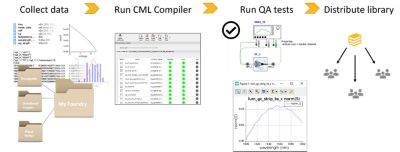

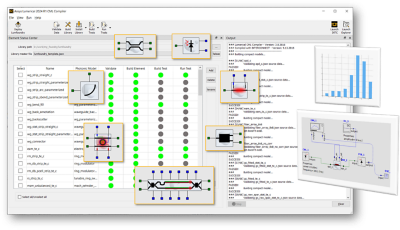

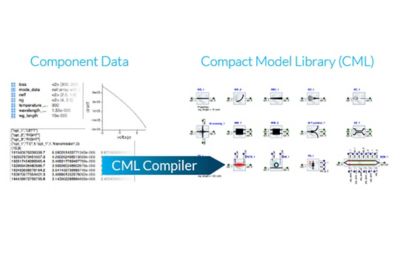

Lumerical CML Compiler의 검증된 안정성을 바탕으로 컴팩트 모델 라이브러리(CML)를 효율적으로 생성합니다. 단일 데이터 소스에서 INTERCONNECT 및 포토닉 Verilog-A 컴팩트 모델 라이브러리(CML)의 생성, 보정, 유지 관리 및 QA 테스트를 자동화하는 소프트웨어입니다. 소스 데이터는 실험 측정, 2D/3D 물리 시뮬레이션 또는 그 조합에서 얻을 수 있습니다.

Lumerical CML Compiler는 측정 또는 시뮬레이션 데이터의 단일 소스에서 고품질 INTERCONNECT 및 포토닉 Verilog-A 컴팩트 모델을 구축할 수 있는 효율적인 방법을 제공합니다.

2025년 1월

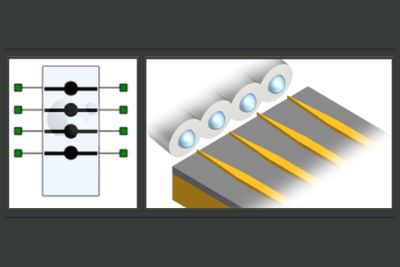

Ansys 2025 R1은 몬테카를로 수율 분석을 통해 정밀한 칩-광섬유 커플링 손실 모델링의 고유한 요소를 위한 사용자 지정 Verilog-A 모델 생성과 광섬유 어레이를 통해 포토닉 설계 기능을 확장합니다.

이 모델을 사용하면 CML Compiler 사용자가 현재 CML Compiler에서 지원하지 않는 고유한, 활성 또는 수동 사용자 지정 요소에 대한 포토닉 Verilog-A 모델을 생성할 수 있습니다. 사용자는 요소의 입력-출력 관계를 정의하기 위해 고유한 Verilog-A 코드를 작성할 수 있습니다.

새로운 광섬유 어레이를 통해 사용자는 칩-광섬유 커플링에서 초과 손실을 모델링할 수 있으며 어레이에서 임의의 수의 Pcell 매개변수와 파이버를 지원합니다. 또한 통계적으로 활성화된 모델은 통계 매개변수 간의 상관 관계를 고려하여 수율 분석을 위해 Monte Carlo 스윕을 지원합니다.

기능

CML Compiler는 측정 및 시뮬레이션 결과의 단일 데이터 소스에서 INTERCONNECT 및 Verilog-A 포토닉 컴팩트 모델 라이브러리(CML)의 생성, 유지 관리 및 QA 테스트를 자동화합니다.

CML Compiler는 포토닉 PDK를 위한 정확한 포토닉 컴팩트 모델 구축을 단순화하여 포토닉 집적 회로 설계를 가능하게 합니다.

Lumerical CTO인 James Pond 박사가 CML Compiler의 시작과 개발 과정부터 OFC 2020에서 시연되는 새로운 통계 분석 및 시뮬레이션 기능까지 설명합니다.

Ansys는 모든 사용자가 당사 제품에 액세스할 수 있다는 것을 가장 중요하게 생각합니다. 따라서 US Access Board(508조), Web Content Accessibility Guidelines(WCAG) 및 Voluntary Product Accessibility Template(VPAT)의 현재 형식에 근거한 접근성 요구 사항을 준수하기 위해 노력하고 있습니다.

엔지니어링 과제에 직면하고 있다면우리 팀이 도와드리겠습니다. 풍부한 경험과 혁신에 대한 헌신을 가지고 있는 우리에게 연락해 주십시오. 협력을 통해 엔지니어링 문제를 성장과 성공의 기회로 바꾸십시오. 지금 문의하기