간단 사양

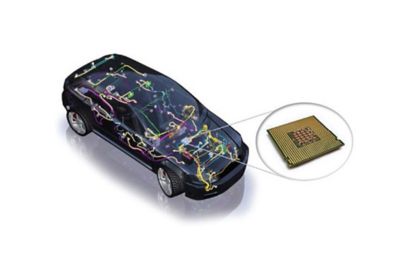

칩 레벨까지 포함한 전체 전자 아키텍처에 걸쳐 기능 안전 분석을 간소화하고 자동화합니다. 기능 안전 분석의 모든 불일치는 제거되고, 확인 검토 및 평가가 가속화됩니다.

Ansys medini analyze는 통합 부품의 IP 설계에서부터 SoC 및 전자 보드에 이르기까지 다양한 칩 레벨에서의 주요 안전 분석 방법을 지원합니다.

Ansys medini anlayze는 반도체 설계의 특정 영역을 전자 아키텍처 내의 주요 기능에 그래픽으로 연결하는 최적화된 워크플로를 지원합니다. 이를 통해 엔지니어는 반도체 부품의 기능 안전을 검증할 때 잠재적 고장 모드를 분석하고 해결할 수 있습니다. 엔지니어는 ISO 26262와 같은 안전 표준에서 요구하는 FMEDA와 같은 안전 관련 활동을 효율적이고 일관되게 실행할 수 있습니다. 2018 part 11.

칩 레벨까지 포함한 전체 전자 아키텍처에 걸쳐 기능 안전 분석을 간소화하고 자동화합니다. 기능 안전 분석의 모든 불일치는 제거되고, 확인 검토 및 평가가 가속화됩니다.

ZF Group Harmonizes and Accelerates Functional Safety Analysis with Ansys medini analyze.

According to Günter Gäbelein, Safety Assessor at ZF Friedrichshafen AG, “As a systems supplier for passenger cars, commercial vehicles, and industrial technology, ZF Friedrichshafen AG places great emphasis on agility and innovation. To support exciting developments like autonomous driving and electric mobility, our R&D process must be fast, cost effective, and technically precise. More and more projects are taking advantage of synergies provided by medini analyze. In a medium-size project, more than 300 hours of effort can be saved by the one-tool solution and the interfaces to third-party tools for architectures. ZF is a strong advocate for model-based engineering, and medini analyze helps to reduce the complexity of analysis for embedded systems."

기능

반도체 안전을 위한 Ansys medini analyze를 사용하여, 하드웨어 설계자와 안전 분석 엔지니어 간에 IP 설계를 원활하게 교환할 수 있습니다. 엔지니어는 하드웨어 설계에 대한 기본 고장율 도출, 설계 데이터(예: 금형 구역, 게이트 수)에 기반한 고장 분포 자동 결정, 하드웨어 설계에 기반한 FMEA, FMEDA, FTA 해석을 수행할 수 있습니다. 팀은 이전 설계의 FMEDA 데이터를 재사용 및 조정하고, 구성 가능한 FMEDA 결과 데이터를 내보내서 안전 데이터를 통합자에게 인계할 수 있습니다.

Ansys medini analyze는 혁신과 제품 신뢰도를 극대화하면서도 개발 비용을 절감하고 출시 시간을 단축하여, 기업이 중요한 경쟁 우위를 달성하는 데 도움을 줍니다.

정성적 방법(예: FMEA, 정량 분석, 고장율 예측, FMEDA 및 진단 범위 분석 또는 FTA)과 종속 고장 분석을 구현합니다. 이러한 방법은 일관된 설계 모델 세트를 통해 다양한 레벨에서 통합 및 수행됩니다.

ISO 26262 반도체 워크플로 Ansys medini analyze는 ISO 26262 준수를 촉진하며, 칩 수준까지 전체 전자 아키텍처에서 기능 안전 분석을 간소화하고 자동화하는 신뢰할 수 있는 솔루션입니다.

IEC 61709, IEC 62380, SN29500 등과 같은 내장 핸드북을 사용하여 칩의 고장율을 예측할 수 있습니다. 영구 및 일시적 장애에 대해 금형 구역 또는 가져온 IP 설계의 요소/게이트/셀 수를 따라 고장율을 분배합니다. 온도와 같은 응력 파라미터를 정의하고 FMEDA 및 PMHF에 대한 영향을 분석하여 안전 및 신뢰성 목표를 달성합니다.

안전 프로젝트를 공유, 비교, 병합하여 안전 엔지니어링 팀으로 협업합니다. 워크플로 지원을 위해 작업 관리 시스템과 통합됩니다. 대상 시스템 컨텍스트에 적응할 수 있도록 현장 팀과 고객에게 맞춤형 방식으로 안전 분석(예: FMEDA)을 내보냅니다.

칩 설계와 함께 안전 요구 사항을 파악하고 추적합니다. 시스템(예: IBM® Rational® DOORS®, PTC Integrity™, Jama Software) 및 설계 툴(Cadence Incitive Simulator 또는 Synopsys IC Compiler)에 대한 요구 사항 관리를 가져오거나 내보내기를 왕복으로 수행합니다. 타사 검증 툴에 의한 결함 주입을 통해 안전 메커니즘의 표준 준수를 검증합니다.

리소스 및 이벤트

장애가 있는 사용자를 포함하여 모든 사용자가 당사의 제품을 쉽게 활용할 수 있는 것은 Ansys에게 중요합니다. 따라서 US Access Board (Section 508), WCAG(Web Content Accessibility Guidelines) 및 현재 VPAT(Voluntary Product Accessibility Template) 형식에 따른 접근성 요구 사항을 준수하기 위해 노력합니다.

엔지니어링 과제에 직면하고 있다면우리 팀이 도와드리겠습니다. 풍부한 경험과 혁신에 대한 헌신을 가지고 있는 우리에게 연락해 주십시오. 협력을 통해 엔지니어링 문제를 성장과 성공의 기회로 바꾸십시오. 지금 문의하기