사양 보기

PathFinder-SC의 통합 데이터 모델링, 추출 및 과도 상태 시뮬레이션 엔진은 ESD 검증을 위한 엔드투엔드 솔루션입니다. 단일 패스 사용 모델은 업계 표준 설계 형식 읽기, ESD 규칙 설정, 전력 네트워크의 RC 추출, ESD 시뮬레이션을 수행하여 근본 원인 분석과 수정 및 최적화된 피드백 제공 등의 모든 작업을 단일 도구로 처리합니다.

Ansys는 학생들에게 시뮬레이션 엔지니어링 소프트웨어를 무료로 제공함으로써 오늘날의 학생들의 성장을 지속적으로 지원하고 있습니다.

Ansys는 학생들에게 시뮬레이션 엔지니어링 소프트웨어를 무료로 제공함으로써 오늘날의 학생들의 성장을 지속적으로 지원하고 있습니다.

Ansys는 학생들에게 시뮬레이션 엔지니어링 소프트웨어를 무료로 제공함으로써 오늘날의 학생들의 성장을 지속적으로 지원하고 있습니다.

Ansys PathFinder-SC는 정전 방전(ESD)에 대비한 무결성과 견고성을 위해 IP 및 풀칩 SoC 설계를 계획하고, 검증하며, 사인오프하는 데 도움이 되는 고용량 솔루션입니다.

Ansys PathFinder-SC는 CDM(Charged-Device Model), HBM(Human Body Model) 또는 기타 ESD 이벤트에서 칩 장애를 일으킬 수 있는 설계 문제의 근본 원인을 식별하고 진단합니다. 대용량 클라우드 기반 아키텍처는 빠른 풀칩 처리를 위해 수천 개의 컴퓨팅 코어를 탑재할 수 있습니다. PathFinder-SC는 주요 파운드리에서 ESD 승인에 대한 저항 및 전류 밀도 검사를 인증받았습니다.

PathFinder-SC의 통합 데이터 모델링, 추출 및 과도 상태 시뮬레이션 엔진은 ESD 검증을 위한 엔드투엔드 솔루션입니다. 단일 패스 사용 모델은 업계 표준 설계 형식 읽기, ESD 규칙 설정, 전력 네트워크의 RC 추출, ESD 시뮬레이션을 수행하여 근본 원인 분석과 수정 및 최적화된 피드백 제공 등의 모든 작업을 단일 도구로 처리합니다.

Lorem Ipsum은 1500년대 이후로 업계의 표준 더미 텍스트였으며, 알 수 없는 인쇄기가 글꼴 교정쇄를 가지고 뒤섞어 글꼴 보기책을 만들었습니다. 뿐만 아니라 5세기 동안 존속되었습니다.

정전 방전 및 전류 밀도는 칩의 실제 견고성과 장기적인 안정성을 결정하는 핵심 요소입니다. 이는 제품 안전 및 내구성에 매우 중요합니다.

낮아진 디바이스 breakdown 전압 및 촘촘한 메탈의 상호 연결구조의 16nm 미만의 프로세스에서 ESD 위험이 증가합니다. PathFinder-SC는 모든 칩 설계에 필요한 온칩 ESD 이벤트에 대한 포괄적인 분석을 제공합니다.

PathFinder-SC는 풀칩 용량 및 간소화된 단일 패스 사용 모델을 통해 한 번의 분석으로 수백 개의 도메인을 동시에 처리할 수 있습니다. 이는 기존의 접근 방식보다 훨씬 빠르며, 결과를 얻는 데 소요되는 시간을 단축하고, 분할로 인한 오류 가능성을 줄입니다.

PathFinder-SC의 레이아웃 기반 분석 및 근본 원인 감지 기술을 사용하여 감지된 문제를 신속하게 디버깅할 수 있으므로 시간이 절약되고 시장 출시 시간이 단축됩니다.

PathFinder-SC는 RC 추출 및 ESD 시뮬레이션 수행부터 근본 원인 분석 및 최적화 피드백 제공에 이르는 모든 기능이 단일 제품에 포함되어 있습니다. 이 제품에는 RC 추출기가 내장되어 있으며 추가 라이선스나 외부 도구가 필요하지 않습니다.

PathFinder-SC는 여러 고객의 실리콘과 상관관계가 있으며 여러 파운드리에서 검증을 받았으므로 정확성이 보장되고 실리콘 위험이 낮아집니다.

Lorem Ipsum은 1500년대 이후로 업계의 표준 더미 텍스트였으며, 알 수 없는 인쇄기가 글꼴 교정쇄를 가지고 뒤섞어 글꼴 보기책을 만들었습니다. 뿐만 아니라 5세기 동안 존속되었습니다.

Ansys PathFinder-SC는 ESD에 대비한 무결성과 견고성을 위해 IP 및 풀칩 SoC 설계를 계획하고, 검증하고, 승인하는 데 도움이 됩니다. CDM(Charged-Device Model), HBM(Human Body Model) 또는 기타 ESD 이벤트에서 칩 또는 IP 장애를 일으킬 수 있는 설계 문제를 파악합니다. PathFinder-SC는 주요 파운드리에서 인증을 받았으며, 상호 연결 기생성, HBM/CDM ESD 시뮬레이션, 저항 및 전류 밀도 검사가 ESD 승인에 필요한 정확성을 갖추었는지 확인합니다. 레이아웃 기반 GUI를 통해 근본 원인을 신속하게 감지하고 쉽게 디버깅할 수 있습니다.

PathFinder-SC는 탄력적인 컴퓨팅과 1억 개 이상의 트랜지스터에 대한 풀칩 분석 처리 기능을 지원하는 클라우드 기반 인프라로 설계되었습니다.

풀 칩 및 포괄적인 단일 패스 ESD 분석, 수백 개의 전력 모드를 동시에 디버깅

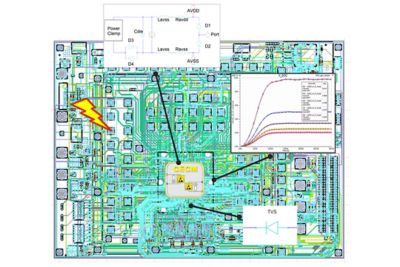

Ansys PathFinder-SC는 레이아웃 병목 현상을 식별하기 위해 전원/그라운드 네트워크를 통해 Zap 전류를 전파하여 HBM(Human Body Model) 및 CDM(Charged-Device Model) ESD 이벤트를 모방합니다. 패드와 상호 연결 경로에 대한 전류 주입을 모델링하여 높은 ESD 전류를 처리할 수 없는 핀-클램프-핀 경로를 식별합니다.

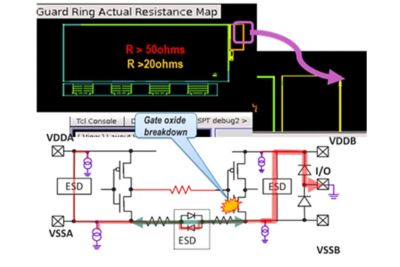

피코 초 해상도의 SPICE 모델 및 TLP 곡선을 사용하는 Ansys PathFinder-SC의 과도 상태 시뮬레이션은 실리콘 관련 정확성을 제공하여 설계 위험을 최소화합니다. 스냅백을 사용하는 클램프는 SPICE에서 수렴 문제가 발생하는 경우가 많습니다. 그러나 PathFinder-SC의 시뮬레이션 엔진은 스냅백을 처리하고 ESD 디바이스 트리거를 정확하게 모델링하도록 맞춤 설정되어 있습니다. PathFinder의 결과는 여러 파운드리 및 고객의 실리콘과 상관관계가 있습니다.

Ansys PathFinder-SC는 ESD 장애를 일으킬 수 있는 레이아웃 문제와 연결 불균형을 식별합니다. 예를 들어 ESD 클램프에 연결되지 않은 범프나 전원/그라운드에 연결되지 않은 클램프가 있습니다. PathFinder-SC는 칩의 두 관련 지점 사이의 모든 전도 경로를 검사함으로써 연결 견고성을 확인하고 파운드리 또는 사용자가 지정한 한계를 기준으로 전기적 특성을 검사합니다. 통과-실패 보고서는 레이아웃에 교차하며 조사할 수 있습니다.

Ansys PathFinder-SC의 통합 데이터 모델링, 추출 및 시뮬레이션 엔진은 단일 도구 환경에서 ESD 규칙 설정, 추출 및 ESD 시뮬레이션 수행, 근본 원인 분석, 수정 및 최적화 피드백 제공 등을 수행하는 간소화된 단일 패스 ESD 사용 모델을 제공합니다. 이는 산업 표준 데이터 형식(GDS, DEF)을 사용하며 검사할 규칙 및 파라미터를 매우 유연하게 지정할 수 있게 해줍니다.

Ansys PathFinder-SC는 1억 개 이상의 인스턴스가 있는 IP 및 대형 SOC에서 ESD 무결성을 검사합니다. 단일 시뮬레이션으로 수백 개의 전원/그라운드/신호 네트워크를 처리하고 저항 및 전류 밀도 검사를 수행합니다. 풀 칩 ESD 시뮬레이션은 크기에 따라 몇 시간에서 하루 안에 완료할 수 있습니다. PathFinder-SC는 초대규모 설계를 처리할 수 있는 탄력적인 컴퓨팅, 클라우드 기반 인프라를 기반으로 합니다.

안정성 문제를 방지하려면 표준 셀 수준, IP 수준 및 풀 칩 수준에서 고전류 핫스팟을 식별하는 것이 중요합니다. PathFinder-SC에 내장된 모델링 기능은 표준 셀부터 풀 칩까지 모든 수준에서 자세한 ESD 분석이 가능한 CECM(Chip ESD Compact Model)을 기반으로 합니다. CECM에는 PG 모델, 클램프 디바이스 및 선택적 전류 서명이 포함됩니다. 이 정확한 모델링은 모든 설계에 대한 최고의 안정성 요구 사항을 충족합니다.

Ansys PathFinder-SC는 수천 개의 CPU 코어에서 클라우드를 실행할 수 있게 설계된 SeaScape 빅 데이터 분석 플랫폼에 기반을 두고 있으며, 준선형적 확장성과 매우 큰 용량, 코어당 낮은 메모리를 제공합니다.

Ansys는 이러한 어려움을 가지고 있는 사용자를 포함하여 모든 사용자가 당사의 제품에 액세스할 수 있는 것이 매우 중요하다고 생각합니다. 따라서 미국 접근성 위원회(508조), WCAG( Web Content Accessibility Guidelines) 및 현재 VPAT(Voluntary Product Accessibility Template) 형식에 따른 접근성 요구 사항을 준수하기 위해 노력합니다.

엔지니어링 과제에 직면하고 있다면우리 팀이 도와드리겠습니다. 풍부한 경험과 혁신에 대한 헌신을 가지고 있는 우리에게 연락해 주십시오. 협력을 통해 엔지니어링 문제를 성장과 성공의 기회로 바꾸십시오. 지금 문의하기