간략한 사양

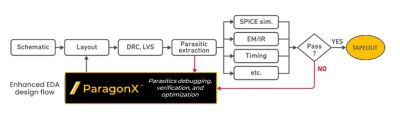

ParagonX는 프로세스에 구애받지 않는 툴로, 설계가 LVS 클린 단계에 도달하기 전인 초기 레이아웃 단계에서도 기생성 관련 설계 문제를 식별할 수 있습니다. 레이아웃 기생성이 미치는 영향을 이해하는 것은 특히 고급 프로세스 노드에서 제조된 설계의 경우 매우 중요합니다. 이를 통해 성능 병목 현상과 설계 프로세스 후반의 약점으로 인한 생산 지연을 방지할 수 있습니다. IC 레이아웃 엔지니어는 대규모 넷리스트를 처리할 수 있는 탁월한 속도와 용량을 통해 근본 원인을 찾고 기생성 문제를 해결할 수 있으므로 설계 품질이 향상되고 설계 주기가 단축됩니다.