-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

Ansys는 학생들에게 시뮬레이션 엔지니어링 소프트웨어를 무료로 제공함으로써 오늘날의 학생들의 성장을 지속적으로 지원하고 있습니다.

-

Ansys는 학생들에게 시뮬레이션 엔지니어링 소프트웨어를 무료로 제공함으로써 오늘날의 학생들의 성장을 지속적으로 지원하고 있습니다.

-

Ansys는 학생들에게 시뮬레이션 엔지니어링 소프트웨어를 무료로 제공함으로써 오늘날의 학생들의 성장을 지속적으로 지원하고 있습니다.

ANSYS 블로그

June 29, 2023

RF 집적 회로(RFIC)란 무엇입니까?

휴대폰 및 무선 인터넷 액세스부터 레이더 및 내비게이션 시스템에 이르기까지 전 세계는 무선 주파수(RF) 전송을 통해 연결되고 있습니다. 기술이 지속적으로 향상됨에 따라 RF 집적 회로(RFIC)는 그 자체로 복잡한 칩이 되었으며 초대형 SoC(System-on-Chip) 솔루션에 통합되었습니다. RFIC는 일반적으로 수백 MHz~수 GHz 범위에서 고주파로 작동하도록 설계되었습니다.

무선 회로 설계의 목적은 높은 비용을 들이지 않고 허용 가능한 품질로 소스와 대상 간에 신호를 송수신하는 것입니다. 이는 검증된 설계 방법을 사용하여 회로를 설계함으로써 목표를 달성할 수 있습니다. RFIC는 일반적으로 증폭기, 필터, 믹서, 발진기 및 변조기/복조기로 통합되어 단일칩으로 구성됩니다.

RF 회로 설계는 저주파 아날로그 설계 기법과 마이크로파 회로 설계에 사용되는 방법을 모두 사용하는 기술입니다. 마이크로파 설계와 저주파 아날로그 설계의 주요 차이점은 T-Line원리의 중요성에 있습니다. 마이크로파 설계는 T-Line 원리에 크게 의존하는 반면, 저주파 아날로그 설계는 그렇지 않습니다. 결과적으로 임피던스 레벨 선택과 신호 크기, 잡음 및 왜곡에 대한 기술이 영향을 받습니다.

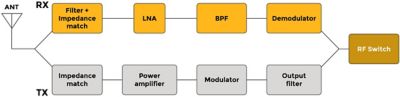

일반적인 무선 주파수(RF) 회로 블록 다이어그램

RFIC 설계의 주요 구성 요소는 다음과 같습니다:

안테나: 무선 주파수 신호를 송수신하는 데 사용됩니다.

필터: 특정 주파수 대역의 신호를 제한합니다. 특정 주파수 범위를 통과하도록 허용하는 대역 통과 필터(BPF), 특정 수준 미만의 주파수를 통과하도록 허용하는 저역 통과 필터(LPF) 또는 특정 수준 이상의 주파수를 통과하도록 허용하는 고역 통과 필터(HPF)가 될 수 있습니다.

임피던스 일치: 소스와 부하 임피던스를 일치시켜 신호 반사를 최소화하거나 전력 전달을 최대화합니다.

저잡음 증폭기(LNA): 수신된 신호가 믹서를 직접 통과할 만큼 강하지 않기 때문에 약한 신호를 증폭하고 잡음 을 필터링합니다.

변조기: 신호 변조에 사용됩니다. 통신 채널 요구 사항을 충족하기 위해 특정 방식으로 신호를 인코딩합니다. 송신기에서 "주파수 상향 변환기" 역할을 하며, 저주파 아날로그 신호를 로컬 발진기 신호와 결합하여 RF 신호를 생성합니다.

복조기: 수신기 측의 신호를 디코딩합니다. 변조된 반송파로부터 원래의 정보 전달 신호를 추출합니다.

전력 증폭기: 전송을 위해 더 높은 전력으로 믹서의 출력을 증폭하는 데 사용됩니다. 적용 범위는 전송 효율성과 함께 증가합니다.

RF 스위치: 전송 경로를 통해 고주파 신호를 라우팅합니다.

RFIC의 사용 사례 및 이점

- 무선 통신 및 연결: RFIC는 휴대폰, 사물 인터넷(IoT) 기기, 가전제품 등의 무선 통신에 널리 사용됩니다. RFIC 지원 기기는 일상 생활의 필수적인 부분이 되었습니다. 소형 크기로의 통합, 전원 관리 및 고속 데이터 전송은 가장 큰 장점 중 하나입니다.

- 자동차 레이더 시스템: RFIC는 충돌 회피, 적응형 크루즈 컨트롤, 주차 지원 등의 용도로 자동차 레이더 시스템에 사용됩니다. 소형 폼 팩터로 차량에 쉽게 장착하여 안전성을 높일 수 있습니다.

- 무선 센서 네트워크: RFIC는 환경 모니터링, 스마트 농업, 산업 자동화 등의 응용 분야를 위한 무선 센서 네트워크에서 활용됩니다. 센서 노드 간의 무선 연결을 통해 많은 케이블 연결과 인프라가 필요 없어집니다. RFIC 기반 애플리케이션을 사용하면 RFIC 기반 네트워크를 쉽게 확장 또는 재구성할 수 있으므로 유연성과 확장성을 확보할 수 있습니다.

- 위성 통신: RFIC는 신호 증폭, 주파수 변환, 변조 등의 작업을 위해 위성 통신 시스템에 사용됩니다. 많은 이점 중에서도 넓은 지원 범위, 높은 데이터 전송 속도, 효율적인 신호 처리를 들 수 있습니다.

최신 RFIC 설계 및 검증

수십 년 동안 아날로그/혼합 신호 설계(AMS)는 예술로 여겨졌으며, RFIC 설계자는 회로도및 레이아웃 단계를 거쳐 물리적 검증 및 회로 시뮬레이션으로 이어지는 매뉴얼 기술을 보유하고 있습니다. 그러나 프로젝트 시간과 예산 측면에서 비용이 많이 듭니다.

이러한 전통적인 설계 및 검증 방법은 최신 RFIC 설계 표준을 충족시키기에는 비효율적입니다. 설계자들이 아날로그, 디지털 및 RF를 대규모 SoC로 통합하려고 시도하고 — 작동 주파수가 계속 증가함에 따라 — 사전에 특성화된 기기 라이브러리나 기타 기존 방법론을 사용하여 RF 집적 회로를 설계하기가 어렵습니다. 또한 고주파에서의 전자기 상호 작용은 신호 반사, 누화및 전자기 장해(EMI)와 같은 기생 효과를 유발하여 회로 성능을 저하시키므로 설계 주기에서 가능한 한 빨리 이를 고려해야 합니다.

최신 RFIC 개발 흐름에서는 각 설계 반복에 대한 처리 시간(TAT)을 단축하는 동시에 최상의 회로 성능을 구현해야 합니다. 따라서 설계와 시뮬레이션은 반복 프로세스에서 함께 진행됩니다. 시뮬레이션 결과에 따라 설계가 여러 번 조정됩니다. 이는 긴 과정이며, 설계자는 매우 촉박한 프로젝트 일정에 맞추기 위해 회로 성능을 일부 절충하기도 합니다. 성능 저하 없이구현하기 위해 RFIC 설계자는 IC 설계에 중점을 둔 고급 전자 설계 자동화(EDA) 툴과 우수한 시뮬레이션 기능을 필요로 합니다.

EDA 툴, 특히 회로도 및 레이아웃 툴과 실리콘 최적화 시뮬레이션 소프트웨어의 원활한 통합은 RFIC 설계를 성공시키는 데 핵심적인 역할을 합니다. 이러한 툴의 하이퍼컨버전스는 실리콘 전용 전자기 솔버를 사용하여 초기 회로도 단계부터 성숙한 레이아웃 단계까지 회로를 빠르고 정확하게 모델링할 수 있을 뿐 아니라 동적 전압 강하, 일렉트로마이그레이션 및 기타 문제에 대한 기본 검사 기능을 제공합니다. Ansys는 Synopsys와 협력하여 최근 RFIC 설계자의 요구 사항을 충족하고 신뢰성과 견고성을 보장하는 통합 솔루션을 제공했습니다.

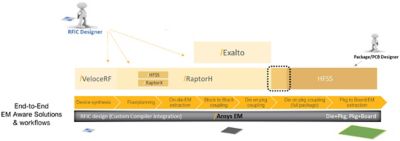

실리콘에 최적화된 Ansys 전자기 시뮬레이션 워크플로는 설계 주기의 초기 단계에서 시작됩니다. Ansys VeloceRF를 사용하면 빠르고 정확한 패시브 디바이스 합성 및 모델링을 구현할 수 있습니다. 플로워플랜 단계에서 정보에 입각한 결정을 내리기 위해 RFIC 설계자는 온칩 설계 및 워크플로만을 위한 전자기 솔버인 Ansys RaptorX를 사용합니다. RaptorX는 모든 패시브 디바이스와 레이아웃의 라우팅을 모델링한 다음, 여러 블록이나 다이와 패키지 간의 결합을 공동 해석할 수 있습니다. RFIC 설계자는 전체 다이, 패키지 및 PCB 전자기 시뮬레이션을 실행할 수 있는 Ansys RaptorH 인터페이스를 통한 시스템 수준의 시뮬레이션을 위해 IC 데이터베이스를 Ansys HFSS에 전달할 수 있습니다. 사인오프 단계에서 Ansys Exalto는 전자기에 중요한 RF 회로의 모든 부분에 대해 전자기 모델을 사용하여 일반 RC 결과를 향상시킵니다. 전자기 모델은 RC 테스트 벤치에서 자동으로 백-어노테이션되어 전자기 신뢰도를 포함한 신속한 레이아웃 후 시뮬레이션이 가능합니다.

RFIC 및 고속 SoC를 위한 Ansys 전자기 인식 워크플로

RFIC 설계를 위한 Ansys의 이 포괄적인 솔루션은 안정성이 높고 견고한 솔루션과 높은 수율을 제공하고 처리 시간을 단축합니다.

VeloceRF, RaptorX, RaptorH 및 Exalto는 설계자가 설계 주기 시간을 여러 차례 단축하고 RFIC 성능을 획기적으로 개선할 수 있도록 지원하는 업계 최고의 전자기 솔루션입니다.

보다 복잡하고 정교한 RFIC를 요구하는 5G와 같이 더 빠르고 안정적인 무선 연결에 대한 수요로 인해 새로운 RF 기술의 개발이 이루어지고 있습니다. 이러한 과제를 해결하기 위해 설계자는 고급 설계 방법, 포괄적인 시뮬레이션 툴 및 최적화된 알고리즘을 사용하여 설계 프로세스를 간소화하고 출시 시간을 단축할 수 있습니다.

RFIC 설계 및 검증 개발을 위한 협력적인 접근 방식을 통해 설계자는 안정적인 고품질 IC를 제공할 수 있습니다. 또한 설계자는 VeloceRF, RaptorX, RaptorH 및 Exalto 솔루션을 활용하여 EDA 설계 툴과의 손쉬운 통합, 정확성 향상, 출시 기간 단축 등을 실현할 수 있습니다.

"RFIC를 위한 실리콘 최적화 전자기 방법론의 기초” 웨비나에서 RF 회로를 위한 Ansys 전자기 방법론의 기초에 대해 자세히 알아보십시오.