-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

-

产品组合

查看所有产品Ansys致力于通过向学生提供免费的仿真工程软件来助力他们获得成功。

-

什么是半导体先进封装?

半导体先进封装,是将多个半导体芯片整合到单个电子封装中的一系列制造工艺。这种方法不仅可以提高性能,同时还能降低功耗和成本。

传统封装就像在一片土地上建造一栋单层建筑,先进封装则实现了在一块面积较小的土地上建造多栋建筑,并使用桥梁、竖井和隧道将其连接起来。有效利用这些技术的公司,将能够在快速增长的半导体市场中获得竞争优势。

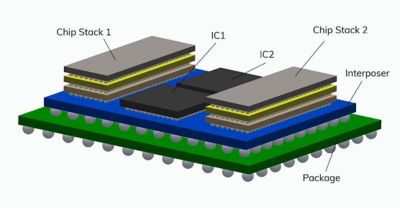

先进封装中最常用的技术有2.5D、3D-IC、异构集成、扇出型晶圆级封装和系统级封装。每种技术都是以不同的方式从晶圆中取出单个芯片,并将其与其他芯片一起放置在一个由塑料、金属或玻璃包围的电气连接组件中——即封装。之后,将封装连接到印刷电路板或柔性胶带上,然后放入电子设备中。

半导体先进封装的优势

随着半导体技术开始“违背”物理定律,我们将更多晶体管封装到更小空间的能力正在减弱。几十年来,微电子行业一直采用英特尔联合创始人戈登·摩尔(Gordon Moore)关于芯片中晶体管的密度每两年翻一番的预测(被称为摩尔定律)来指导其投资和规划,以跟上这一发展步伐。这推动着每一代芯片的特征尺寸变得更小、密度更高,设备中的电气连接也因此成为性能瓶颈。 。

而先进封装是设计人员克服这一限制的强大方法。通过在三维空间中布置多个芯片,并在芯片之间和过渡集成电路中直接建立连接,他们可以消除瓶颈并降低成本。该方法的另一个优势是,通过将具有不同功能的芯片放置在邻近位置,从而降低功耗、提高速度并将多功能器件简化为单个封装。

这种单个封装的形式,还能降低制造、运输和库存成本,因为它将集成从涉及多个组件的后处理步骤,转移到了半导体制造现场(也称为晶圆厂)的前端步骤。此外,这种方法还显著降低了封装劳务成本,因为无需寻找劳动力成本较低的地方来建立单独的封装设施。

使用半导体先进封装模块的设备应用

随着人们对计算能力和存储所有数据的内存需求不断增长,人们需要更高效、更低成本的微电子设备。消费类电子产品日益复杂、功能越来越强大,需要以更低功耗在更小封装中实现更强的功能。同时,越来越多的设备变得更加智能,设备中增加了测量(传感器)、导入数据、计算(处理器)、存储数据(内存)或导出数据的组件。先进封装可以帮助产品将每种功能的多个单元整合到单个模块中。

其中一个增长最快的领域是汽车行业。性能、效率和安全性方面的先进系统,加上不断增加的传感器数量,都对采用先进封装制造的更可靠、更高效且成本更低的电子模块提出更高要求。

另一方面,物联网(IoT)设备领域的产品设计人员,也希望将多项电子功能组合在单个部件中,以添加到其电子设计中。使用先进封装创建的解决方案可简化装配自动化和PCB的复杂性,同时提高性能并降低成本和功耗需求。

先进封装有助于满足人工智能(AI)和高性能计算(HPC)的密集计算需求。这种方法可在尺寸更小、功耗更低的配置中提供更多功能。AI和HPC硬件提供商(如NVIDIA)已建立了先进的封装供应链,并采用英特尔和台积电的先进封装功能来生产所需的多功能模块,以提高性能,同时控制功耗需求和成本。

先进封装组件和技术

先进的半导体封装使用多种技术更高效地将IC芯片组合在封装中。

了解先进封装的一个好办法,是查看其组件以及半导体代工厂使用的各种先进封装技术。

组件

- 芯粒(Chiplet):针对特定功能进行优化的未封装离散裸片,在封装级与其他芯粒和多功能IC芯片组合在一起。

- 裸片(Die):从较大的晶圆上切割下来的半导体材料块,其中包含设计用于执行一种或多种功能的电路。 当裸片连接到基板或其他裸片时,它们就会成为芯片。

- I/O焊盘或凸点:芯片表面的导电区域,用于向芯片内部或外部发送信号。

- 互连:连接两个或多个电路元件以在它们之间传输电流的结构。它通常是连接一个或多个裸片的薄型结构。

- 硅中介:一个或多个芯片和基板之间的一层材料。在先进封装中,该材料可以是硅基材料或玻璃基材料。

- 印刷电路板(PCB):一种带有多层电路的平面结构,其可以是刚性的,也可以是柔性的,用于将电子系统中的组件进行电气连接。它们通常由FR4(刚性)或聚酰胺(柔性)制成。

- 再分布层(RDL):一个或多个裸片下的额外金属化层,包含内部传导路径,可创建更有利的I/O焊盘。

- 焊球:用于连接半导体封装组件的小焊球。其尺寸因连接的组件而异。

- 基板:一种包含电路的平面组件,用于将封装中的其他组件进行物理连接和电气连接。IC基板是一层半导体材料,其是由FR4或聚酰胺制成的层压基板。

- 片上系统(SoC):一种IC芯片,将所有计算机或电子系统功能集成在单个芯片上。

- 硅通孔(TSV):硅晶圆或裸片顶部和底部之间的电气连接。是由薄型半导体材料构建的组件之间的互连。

- 引线键合:裸片和基板之间(或多个裸片之间)的引线。这种成本相对较低的封装组件连接方法在传统封装中占主导地位。

技术

2.5-D堆栈使用带TSV的硅中介将多个芯片连接到封装,3D堆栈使用裸片中的TSV垂直堆叠裸片。

- 2.5-D:2.5-D技术是在裸片和基板之间使用硅中介,而非将多个裸片连接到IC基板。硅中介使用TSV通过硅中介传递信号。

- 3D-IC:一种将多个裸片相互叠放的方法。TSV可用于连接裸片。

- 扇出型晶圆级封装:采用RDL(重布线层)工艺,从芯片上的密集I/O焊盘过渡到基板上更大的球栅阵列。

- 系统级封装(SiP):采用2.5D或3D-IC技术生产完整的计算机或电子器件封装。SiP不是将SoC解决方案所需的所有IC放置在一起,而是将多个裸片组合在单个封装中,以实现相同的行为。

半导体先进封装面临的挑战

从打包行李箱到创建最新的GPU模块,封装行为都是为了尽可能高效地将您所需的一切装在一定空间中。对于先进半导体应用,您还必须在保证成本目标的同时处理电源完整性、信号完整性、热完整性和机械应力问题。

互连

封装中的每个芯片都需要连接到I/O焊盘,这些焊盘将模块连接到电子设备的其余部分。封装中必须设计传导路径,例如互连、TSV或电线。由于它们携带信号,因此必须检查每条路径,以确保其信号不会干扰邻近的信号,也不会过热。

功耗

电源效率是催生市场差异化的一个因素。客户希望以更低的功耗完成更多的工作,因此封装设计人员必须开发配置并利用能够最大限度降低功耗和损耗的技术。

热

当施加电流时,封装中的每个组件都会产生热量。封装需要热管理解决方案,利用配置和材料最大限度地减少热积聚,将热量从组件中传输出去,以及消除热量对设备的影响。

鲁棒性

当封装升温和冷却时,材料会膨胀和收缩。设计人员必须使用各种材料和互连技术,以确保每种材料的膨胀差异以及反复的膨胀和收缩不会导致任何互连或芯片出现故障。焊球疲劳和封装设计还必须在汽车、物联网和航空航天等应用中的恶劣环境下经受住磨损。

成本

在竞争激烈的半导体行业中,成本是一个主要驱动因素。传统芯片封装作为后端工艺封装,可能需要大量人力还有运输成本。先进封装流程必须利用自动化,并将封装转变为前期流程(包括集成测试)的一部分。设计人员通常利用优化工具,在考虑成本的同时明智地选择他们的方案。

半导体先进封装的未来

在半导体供应链的上下游,各公司都在开发路线图,其中包括更先进的封装、更高的性能和更低的成本。Yole Intelligence最近的一项研究发现,2022年,先进封装在市值920亿美元的行业中占比48%。该报告预测,到2028年,这一份额将在市值1,360亿美元的行业中增长到58%。

新一代封装制造必须利用新材料、更高的自动化程度和创新技术,以满足人们对节能且低成本的封装、更紧凑的芯片设计和片内系统应用日益增长的需求。

各国和各公司之间在封装生态系统中的竞争将十分激烈。根据2023年芯片法案(CHIPS Act),国家先进封装制造计划将获得30亿美元的资金。行业领导者英特尔、台积电和Amkor分别宣布,在2023年投资35亿美元、29亿美元和20亿美元,用于开发新的先进封装设施。

除了制造工厂的技术外,工程师还将寻找更好的软件工具,以支持可集成到设计工作流程中的特定封装技术。例如,Ansys、微软和台积电最近合作开发了基于云的2.5D/3D-IC封装应力仿真工具集。

相关资源

现在就开始行动吧!

如果您面临工程方面的挑战,我们的团队将随时为您提供帮助。我们拥有丰富的经验并秉持创新承诺,期待与您联系。让我们携手合作,将您的工程挑战转化为价值增长和成功的机遇。欢迎立即联系我们进行交流。