快速规格

Ansys VeloceRF使您能够对紧密封装了多个器件和线路的器件进行合成,从而实现优化的芯片平面布置图。在详细布局之前对任意数量的感应器件之间的耦合进行分析,将减小设计尺寸并减少或消除护环。

产品组合

查看所有产品Ansys致力于通过向学生提供免费的仿真工程软件来助力他们获得成功。

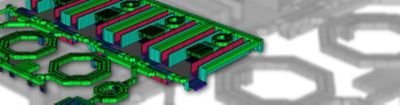

Ansys VeloceRF可显著减少用于合成与建模复杂螺旋器件和T线的时间,从而缩短设计周期。编译电感或变压器的几何结构仅需几秒钟,而对其进行建模和分析只需几分钟。它与领先的EDA平台集成,可实例化用于流片的布局。

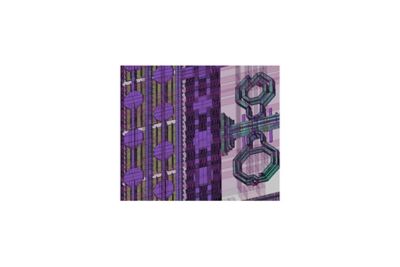

Ansys VeloceRF使您能够对紧密封装了多个器件和线路的器件进行合成,从而实现优化的芯片平面布置图。在详细布局之前对任意数量的感应器件之间的耦合进行分析,将减小设计尺寸并减少或消除护环。

Ansys VeloceRF可显著减少用于合成与建模复杂螺旋器件和T线的时间,从而缩短设计周期。

电感尺寸以及电感之间的串扰会影响芯片尺寸。Ansys VeloceRF可通过使用优化标准和几何约束来帮助您设计较小的器件。此外,它还可以计算任意数量的电感之间的耦合,以便更好地优化芯片基板面积并优化电路环境中的电感。Ansys VeloceRF的参数扫描支持功能可在电路环境中提供最佳性能的解决方案。经过代工厂验证的精度可降低设计中的风险,而经过硅验证的模型有助于消除串扰故障。

Ansys VeloceRF目前支持200多种独特的代工厂工艺,并适用于任何低至3nm的工艺,其中包括来自所有半导体代工厂(台积电、UMC、Global Foundries、TowerJazz和三星等)的CMOS、BiCMOS、GaAs、SOS和SOI。该工具可与领先的EDA设计平台和任何LVS工具集成。

Ansys VeloceRF只需几分钟即可合成和建模毫米波螺旋器件和T线。它可产生DRC/DFM检查器件——包括填充至3nm。这些器件采用无源、因果S参数和高度紧凑的RLCk网表模型进行建模,并且可作为PCell/PyCell提供,以实现最大的几何灵活性。情景优化通过对多个器件和生产线进行紧凑的平面布置图封装以及减少或消除保护环,可以显著减小芯片尺寸。它通过预定义的器件构建模块库支持高频,并支持任意数量的感应器件之间的耦合。

VeloceRF提供硅上感应器件的全面hecheng、建模、分析和优化。

所有用户(包括残障人士)都可以访问我们的产品,这对Ansys至关重要。因此,我们努力遵循基于美国访问委员会(Section 508)、网页内容无障碍指南(WCAG)和自愿产品可访问性模板(VPAT)的当前格式的可访问性要求。

如果您面临工程方面的挑战,我们的团队将随时为您提供帮助。我们拥有丰富的经验并秉持创新承诺,期待与您联系。让我们携手合作,将您的工程挑战转化为价值增长和成功的机遇。欢迎立即联系我们进行交流。