Quick Specs

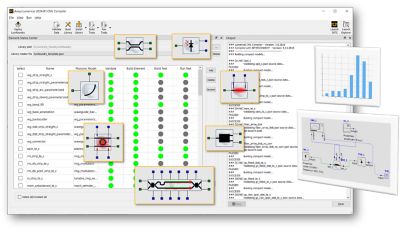

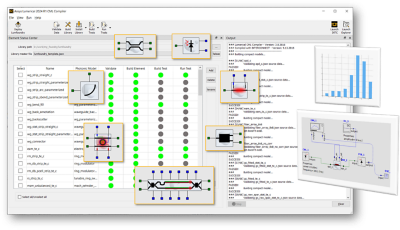

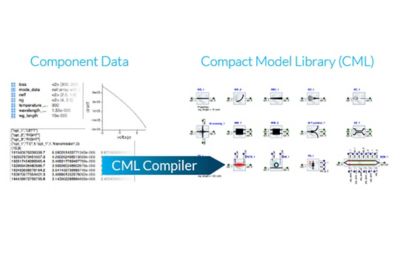

Lumerical CML Compiler offers an efficient way to build high-quality INTERCONNECT and photonic Verilog-A compact models from a single source of measurement and/or simulation data.

Automatically build compact model libraries (CMLs) with a proven, automated, cross-platform model generator using the Ansys Lumerical CML Compiler.

Build and Maintain CMLs with Confidence

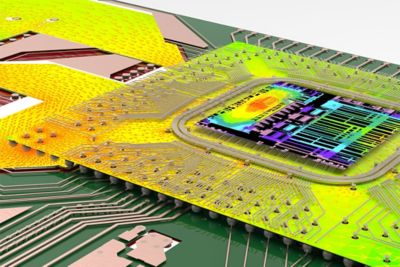

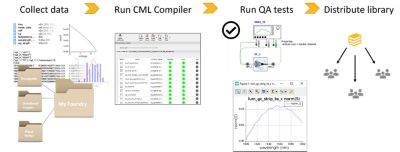

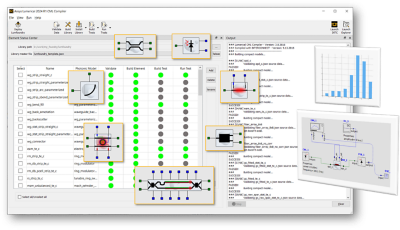

Efficiently create compact model libraries (CMLs) with the proven reliability of Lumerical CML Compiler. The software automates the creation, calibration, maintenance, and QA testing of INTERCONNECT and photonic Verilog-A compact model libraries from a single data source. The source data can come from experimental measurement, 2D/3D physical simulation, or a combination thereof.

Lumerical CML Compiler offers an efficient way to build high-quality INTERCONNECT and photonic Verilog-A compact models from a single source of measurement and/or simulation data.

March 2026

The 2026 R1 release of Ansys Lumerical CML Compiler introduces IBIS-AMIreduced order models, a user-friendly built-in Model Data Editor, and the ability toautomate tools with PyLumerical.

Introducing an innovative solution for generating IBIS-AMI models using machine learning. Photonic engineers can now create reduced-order models with Lumerical INTERCONNECT, enabling system designers to perform precise Signal Integrity analysis and high-speed interface simulations with confidence.

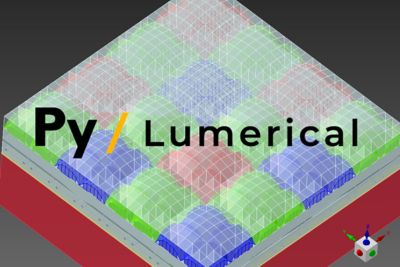

Automate Lumerical tools seamlessly with PyLumerical, a Python-based solution. Fully compatible with the PyAnsys ecosystem, it integrates with FDTD, MODE, Multiphysics, INTERCONNECT, and other Ansys tools like Optislang and Speos, plus open-source Python libraries. Simplify workflows and enhance multiphysics simulations with this modern, efficient approach.

The Built-in Model Data Editor in Ansys Lumerical CML Compiler offers an interactive user-friendly interface to view and edit data directly in the GUI. It features simultaneous multi-tab editing with integrated matrix and vector editors, making it an ideal tool for handling diverse photonic models and perfect for new users starting with CML Compiler.

CAPABILITIES

CML Compiler automates the creation, maintenance, and QA testing of INTERCONNECT and Verilog-A photonic compact model libraries (CMLs) from a single data source of measurements and simulation results.

CML Compiler simplifies building accurate photonic compact models for your photonic PDK, enabling photonic integrated circuit design.

Lumerical CTO, Dr. James Pond, walks us through the origin and development of the CML Compiler all the way to the new Statistical Analysis and Simulation functionality being demonstrated at OFC 2020.

It's vital to Ansys that all users, including those with disabilities, can access our products. As such, we endeavor to follow accessibility requirements based on the US Access Board (Section 508), Web Content Accessibility Guidelines (WCAG), and the current format of the Voluntary Product Accessibility Template (VPAT).

如果您面临工程方面的挑战,我们的团队将随时为您提供帮助。我们拥有丰富的经验并秉持创新承诺,期待与您联系。让我们携手合作,将您的工程挑战转化为价值增长和成功的机遇。欢迎立即联系我们进行交流。