-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

Ansys는 학생들에게 시뮬레이션 엔지니어링 소프트웨어를 무료로 제공함으로써 오늘날의 학생들의 성장을 지속적으로 지원하고 있습니다.

-

Ansys는 학생들에게 시뮬레이션 엔지니어링 소프트웨어를 무료로 제공함으로써 오늘날의 학생들의 성장을 지속적으로 지원하고 있습니다.

-

Ansys는 학생들에게 시뮬레이션 엔지니어링 소프트웨어를 무료로 제공함으로써 오늘날의 학생들의 성장을 지속적으로 지원하고 있습니다.

MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor) 게이트 저항은 특히 고주파의 고급 반도체 노드(16nm 이하)에서 매우 중요한 파라미터입니다. 게이트 저항은 다음과 같은 MOSFET 및 CMOS(Complementary Metal-Oxide-Semiconductor) 회로의 다양한 특성을 결정합니다.

- 스위칭 속도

- RC(저항-커패시터) 지연

- Fmax - 최대 진동 주파수

- 게이트(열) 소음

- MOS 커패시터 및 바랙터(전압 제어 커패시터)의 직렬 저항 및 품질 계수

- 전력 전계효과 트랜지스터(FET)의 스위칭 속도 및 균일성

그러나 이러한 노드에서는 기생 저항, 커패시턴스 및 인덕턴스 등의 복잡한 문제로 인해 게이트 저항의 실제 크기를 결정하기가 어렵습니다. 기생 효과는 설계의 레이아웃 및 재료의 물리적 결함으로 인해 회로 설계에 존재하는 원치 않는 저항, 커패시턴스 또는 인덕턴스 효과입니다. 기생은 전력 손실과 발열을 유발할 수 있으며 신호 품질도 저하시킵니다. 게이트의 작동을 더 잘 이해하려면 모델에서 이러한 기생 효과를 추출하여 저항, 커패시턴스 및 인덕턴스의 실제 값을 얻는 것이 중요합니다.

Ansys ParagonX 집적 회로 레이아웃 기생 분석 및 디버깅 소프트웨어와 같은 특수 전자 설계 자동화(EDA) 툴을 사용함으로써 SPEF(표준 기생 교환 형식, IEEE 표준) 및 DSPF(방위 보안 원칙 프레임워크)를 비롯한 사후 레이아웃 넷리스트에 대한 저항-커패시터(RC) 네트워크 연결을 시각화하여 게이트 저항을 분석할 수 있습니다. 이러한 툴은 넷리스트를 조사하여 R 및 C 값을 확인하고 검사하며 기타 전기 분석을 수행할 수 있습니다. SPICE 모델도 유용할 수 있지만, 기생 R 및 C 값을 계산하는 데 있어 기생 추출이 더 정확한 방법으로 간주됩니다. 이는 레이아웃 정보를 기반으로 하기 때문입니다.

게이트 저항에 관한 많은 논문이 작성되었습니다. 그러나 IC 설계자 및 레이아웃 엔지니어의 실제 작업에서는 몇 가지 중요한 사항이 논의되거나 설명되지 않았습니다.

- 기생 추출 툴은 게이트 저항을 어떻게 처리합니까?

- 레이아웃에서나 추출된 사후 레이아웃 넷리스트에서 게이트 저항을 어떻게 평가할 수 있습니까?

- 게이트 저항이 "고유" 게이트 저항(게이트 폴리) 또는 게이트 금속화 라우팅에 의해 제한되는지 어떻게 식별할 수 있습니까? 그리고 가장 중요한 계층과 다각형은 무엇입니까?

- 프로세스 설계 키트(PDK)의 IC 설계 흐름에서 게이트 분산 효과(단일 접촉 및 이중 접촉 폴리의 경우 각각 1/3 및 1/12 계수)가 포착됩니까?

- 수직 게이트 저항 구성 요소가 파운드리 PDK에 캡처됩니까?

- 게이트 저항을 줄이기 위해 게이트를 더 넓게 또는 더 좁게 만들어야 합니까?

여기서는 논의가 부족한 이러한 문제를 조명하고 IC 설계 및 레이아웃 엔지니어가 설계의 게이트 저항을 더 잘 이해할 수 있도록 통찰력을 제공하려고 합니다.

게이트 저항 정의 및 측정

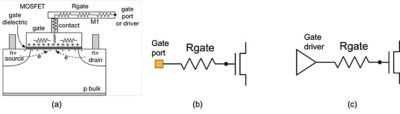

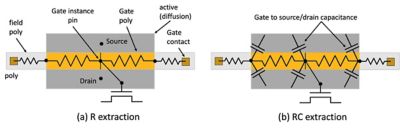

게이트 저항은 그림 1과 같이 구동 지점(예: 게이트 포트 또는 게이트 드라이버)에서 MOSFET 게이트 인스턴스 핀까지의 "유효" 저항입니다. 인스턴스 핀은 SPICE 모델 터미널과 저항성 네트워크 사이의 연결점입니다.

그림 1. 게이트 저항의 MOSFET 단면 및 개략도

그러나 그림 1의 개요도가 단순하여 오해의 소지가 있을 수 있습니다. 게이트 네트는 매우 클 수 있으며 그림 2와 같이 많은 구동 지점, 수십 개의 계층(금속 및 비아), 수백만 개의 다각형 및 최대 수백만 개의 게이트 인스턴스 핀을 포함할 수 있습니다.

그림 2. MOSFET 게이트 네트워크 평면도 및 단면도의 개략도

게이트 네트워크는 하나 또는 여러 개의 구동 지점과 많은 대상 지점이 있는 대규모 분산 시스템입니다. 이 시스템은 거대한 일반 클록 네트워크와 유사하게 보이고 작동하여 게이트 전압을 FET에 분배합니다. 이처럼 크고 복잡한 시스템에 대해 동등하고 효과적인 게이트 저항을 도출하는 것은 간단하고 쉬운 작업이 아닙니다. SPICE 회로 시뮬레이션은 게이트 저항 값을 명시적으로 보고하지 않으므로 기생 추출 툴이 필요합니다.

기생 추출 툴에 의한 게이트 저항 처리

산업 표준 기생 추출 툴은 모두 게이트 저항과 추출을 유사하게 처리합니다. 레이아웃에서 MOS 게이트 구조는 복잡한 게이트 금속 스택에 의해 재료가 형성될 수 있고 복잡한 3D 구조를 가질 수 있음에도 불구하고 전통적으로 "폴리"(폴리실리콘)라고 하는 2D 마스크로 표현됩니다.

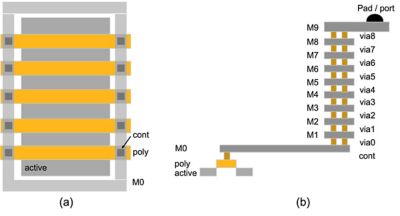

추출 툴은 기본적으로 활성(확산) 층(그림 3의 어두운 회색 음영 영역)과의 교차점에서 폴리 선을 분리합니다. 이렇게 하면 분석을 위한 두 섹션이 생성됩니다. "게이트 폴리"(활성 영역의 폴리, 노란색 음영 영역) 및 "필드 폴리"(활성 영역 외부의 폴리, 밝은 회색 음영 영역). 폴리와 활성 영역은 모두 트랜지스터를 구성합니다.

그림 3. MOSFET 게이트 주변의 R 및 RC 추출

게이트 폴리(노란색 음영 영역)도 중심점에서 파단되고, MOSFET(SPICE 모델)의 게이트 인스턴스 핀이 게이트 폴리의 중심점(노란색 음영 영역의 중앙에 있는 검은색 수직선)에 연결됩니다. 게이트 폴리는 파단 지점을 연결하는 두 개의 기생 저항으로 표현됩니다. 필드 폴리를 나타내는 기생 저항은 게이트 접점 또는 MEOL(상호 연결 금속/비아로 구성된 중간-종단 라인) 층에 연결되고 더 나아가 상위 금속 층에 연결됩니다.

게이트 폴리와 소스/드레인 확산 및 접점 사이의 MOSFET 외부 기생 커패시턴스는 기생 추출 툴로 계산되고 저항성 네트워크의 노드에 할당됩니다. 게이트 저항 네트워크에 대한 기생 커패시턴스 연결의 세부 사항은 특히 게이트 기생 저항이 높은 고급 노드에서 과도 및 AC 응답에 크고 중요한 영향을 줄 수 있습니다.

이러한 세부 사항은 DSPF 파일에서 볼 수 있지만 일반적으로 공개 문서나 파운드리 PDK 설명서에서는 다루지 않습니다. 텍스트 DSPF 파일의 육안 검사는 지루한 작업이며 전문 지식이 필요합니다. ParagonX 애플리케이션과 같은 시뮬레이션 소프트웨어를 사용하면 사후 레이아웃 넷리스트(예: DSPF, SPEF)의 RC 네트워크 연결을 시각화하고, R 및 C 값을 검사하고, 전기 분석을 수행하고, 기타 유용한 작업을 수행할 수 있습니다.

차수 감소 게이트 모델

그림 4와 같이 MOSFET 게이트는 게이트 너비를 따라 대규모 분산형 RC 네트워크를 형성합니다.

그림 4. 게이트 너비에 따른 게이트의 분산 속성 및 모델

이 분산 네트워크는 단순한 집중형 1-R 및 1-C 회로와 다른 AC 및 과도 응답을 갖습니다. 연구원들은 이와 같은 RC 네트워크가 하나의 R 요소와 하나의 C 요소가 있는 네트워크와 거의 동일하게 동작한다는 것을 보여주었습니다.1 여기서

- C는 총 커패시턴스입니다.

- 단면 연결 폴리의 경우 R=1/3 * W/L * rsh입니다.

- 양면 연결 폴리의 경우 R=1/12 * W/L * rsh입니다.

이때 W는 너비, L은 길이, rsh는 폴리의 시트 저항입니다. 계수(1/3 및 1/12)는 게이트에 대한 정확한 차수 감소 모델을 효과적으로 구현하여 많은 수의 R 및 C 요소를 두 개(또는 세 개)의 저항과 하나의 커패시터로 줄입니다. 차수 감소 모델을 사용하면 기생 추출 소프트웨어에서 수행하는 계산을 단순화하고 가속화할 수 있습니다.

상호 연결 기생이 게이트 저항에 미치는 영향

이전 노드 기술에서는 금속과 비아와 같은 금속 상호 연결의 저항이 매우 낮았으며 게이트 저항이 게이트 폴리에 의해 좌우되었습니다. 게이트 저항의 분석 및 계산은 매우 간단했습니다.

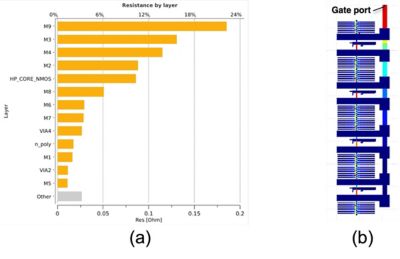

기술이 16nm 이하에 도달하면 상호 연결은 매우 높은 저항을 가지며 게이트 저항에 크게(50% 이상) 영향을 미칠 수 있습니다. 레이아웃에 따라 게이트 저항은 트랜지스터(예: 게이트 폴리 또는 필드 폴리), MEOL 또는 후면부(BEOL, 두꺼운 금속 및 패시베이션 층이 있는 최상층으로 구성) 등 모든 계층에서 중요한 역할을 할 수 있습니다.

그림 5는 ParagonX 소프트웨어를 사용한 게이트 저항 시뮬레이션의 결과를 보여줍니다. 계층별 저항 기여도가 있는 파레토 차트(그림 5a)는 게이트 저항의 가장 중요한 계층을 식별하는 데 도움이 됩니다. 레이아웃 다각형별 게이트 저항 기여도(그림 5b)를 시각화하면 레이아웃 최적화 작업을 안내하는 데 매우 유용한 초크 포인트 또는 게이트 저항에 대한 병목 지점을 즉시 알 수 있습니다.

그림 5. 게이트 저항의 시뮬레이션 결과: (a) 계층별 게이트 저항 기여도, (b) 레이아웃에 색상으로 표시된 다각형별 기여도

FinFET의 게이트 저항

평면 MOSFET에서 게이트의 구조는 매우 단순한 평면이며 게이트 전류 흐름은 게이트 너비의 방향을 따라 1차원입니다.

FinFET(Fin Field-Effect Transistor) 기술에서는 게이트가 매우 높은 실리콘 핀 주위를 감싸므로 복잡한 3D 구조로 이어집니다. 또한 게이트 재료는 작업 기능 또는 고체에서 고체 표면 바로 바깥의 진공 지점까지 전자를 제거하는 데 필요한 최소 열역학 작업을 기반으로 선택되어 임계 전압을 조정합니다. FinFET의 임계 전압은 채널 도핑이 아니라 게이트 재료에 의해 조정됩니다. 이러한 재료는 저항이 매우 높으며, 요청된 폴리(일반적인 시트 저항이 ~10ohm/sq)보다 훨씬 높습니다. 또한 게이트는 실리콘이 있는 인터페이스 계층과 그 위에 하나 이상의 계층 등 다중 계층으로 형성될 수 있습니다.

그러나 기생 추출 소프트웨어를 사용하면 IC 설계자와 레이아웃 엔지니어에게 이러한 모든 세부 사항을 숨길 수 있습니다. 그들은 "폴리"와 "활성"에 대한 일반적인 다각형을 볼 수 있으므로 설계 작업이 훨씬 쉬워집니다.

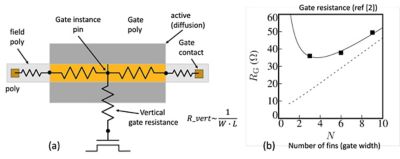

게이트 저항의 수직 구성 요소

16nm 이전 기술에서 게이트 저항은 측면 저항에 의해 좌우되었습니다. 그러나 첨단 기술에서는 게이트 재료 계층 간의 다중 인터페이스로 인해 수직 게이트 저항이 커집니다. 이 저항은 게이트 폴리 면적에 반비례합니다. 그림 6a와 같이 게이트 인스턴스 핀을 게이트 폴리의 중심점에 연결하는 추가 저항으로 모델링할 수 있습니다. 그 결과, 게이트가 좁아지면(예: 핀 수가 더 적음) 게이트 저항은 감소하지만 게이트 폭이 매우 작으면 그림 6b에서 볼 수 있듯이 게이트 저항이 증가합니다.2 특유의 단조롭지 않은 동작을 보입니다. "게이트가 좁을수록 게이트 저항이 낮다"는 기존의 경험 법칙은 더 이상 유효하지 않습니다. 설계자와 레이아웃 엔지니어는 게이트 저항을 최소화하기 위해 최적(비최소) 게이트 너비(핀 수)를 선택해야 합니다.

그림 6. (a) 수직 게이트 저항을 고려한 게이트 모델, (b) 측정 및 시뮬레이션된 게이트 저항과 핀 수([2])

기술 동향

지금까지 살펴본 바와 같이, 기술이 점점 더 작은 노드(현재 최저 2nm에 달함)로 확장됨에 따라 게이트 저항과 상호 연결 저항이 모두 1~2배까지 크게 증가합니다. 따라서 이전 노드의 게이트 저항에는 중요하지 않았던 레이아웃의 세부 사항이 고급 노드에서 매우 중요해집니다. 노드에 따라 디바이스의 크기가 계속 감소함에 따라 이러한 추세는 지속될 것입니다. SPICE 모델은 더 이상 이러한 수준에서 효과적이지 않기 때문에 해당 수준에서 동등하고 효과적인 게이트 저항 값을 이해하려면 ParagonX 소프트웨어와 같은 기생 추출 소프트웨어가 필요합니다.

IC 설계 흐름을 개선할 수 있는 ParagonX 소프트웨어에 대해 자세히 알아보십시오.

참고 자료

1. B. Razavi, et al., "Impact of distributed gate resistance on the performance of MOS devices," IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 41, pp. 750-754, 11 1994.

2. A.J.Sholten et al., "FinFET compact modelling for analogue and RF applications," IEDM 2010, p. 190.

Advantage 블로그

Ansys 및 기타 기술 전문가의 지식을 담은 Ansys Advantage 블로그에서는 인간의 발전을 이끄는 혁신을 뒷받침하고 있는 Ansys 시뮬레이션에 대한 최신 정보를 제공합니다.