规格速览

Lumerical CML Compiler提供了一种高效的方法,可通过测量和/或仿真数据的统一来源,构建高质量INTERCONNECT和光子Verilog-A紧凑模型。

产品组合

查看所有产品Ansys致力于通过向学生提供免费的仿真工程软件来助力他们获得成功。

充满信心地构建和维护CML

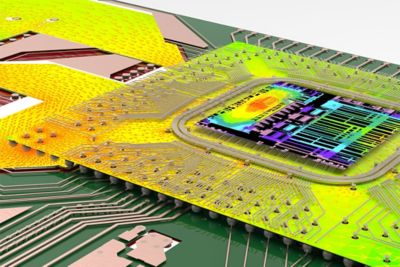

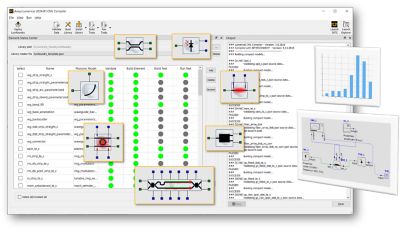

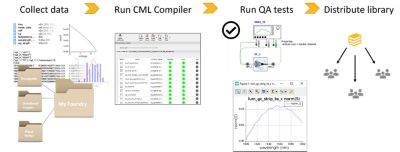

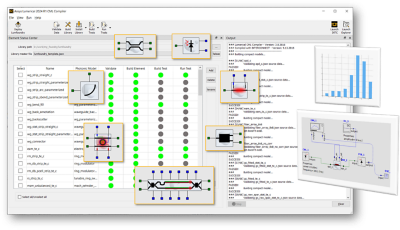

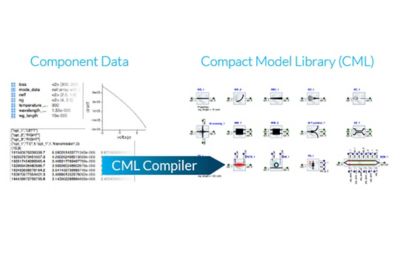

利用Lumerical CML Compiler经过验证的可靠性能高效创建紧凑模型库(CML)。该软件可从单一数据源自动创建、校准、维护和质量保证测试 INTERCONNECT 和光子 Verilog-A 紧凑型模型库。源数据可以来自实验测量、2D/3D物理仿真或两者的结合。

Lumerical CML Compiler提供了一种高效的方法,可通过测量和/或仿真数据的统一来源,构建高质量INTERCONNECT和光子Verilog-A紧凑模型。

2025年1月

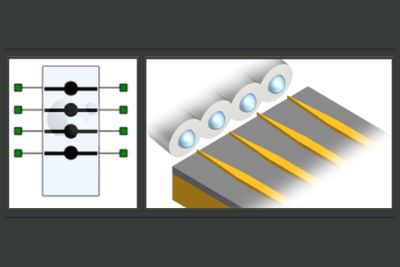

Ansys 2025 R1扩展了光子设计功能,为独特元件和光纤阵列带来了自定义Verilog-A模型创建,从而可通过蒙特卡罗良率分析实现精确的芯片至光纤耦合损耗建模。

该模型允许CML Compiler用户为当前不支持的任何独特、主动或被动自定义单元创建光子Verilog-A模型。用户可以编写自己的Verilog-A代码来为单元定义输入输出关系。

最新光纤阵列不仅可帮助用户为芯片至光纤耦合的超额损耗建模,而且还支持阵列中任意数量的Pcell参数和光纤。此外,统计功能的模型还可为良率分析提供蒙特卡罗扫描,考虑统计参数之间的相关性。

功能

根据测量结果和仿真结果构成的统一数据源,CML Compiler可对INTERCONNECT和Verilog-A光子紧凑模型库(CML)进行自动创建、维护和QA测试。

CML Compiler简化了为光子PDK构建精确光子紧凑模型的流程,可实现光子集成电路设计。

Lumerical首席技术官James Pond博士将向我们介绍CML Compiler的起源和发展,以及在OFC 2020上展示的新统计分析功能和仿真功能。

要让包括残障人士在内的所有用户都能访问我们的产品,这一点对于Ansys而言至关重要。因此,我们始终致力于遵循基于美国访问委员会(第508节)、Web内容可访问性指南(WCAG)和当前自愿产品可访问性模板(VPAT)格式的可访问性要求。

如果您面临工程方面的挑战,我们的团队将随时为您提供帮助。我们拥有丰富的经验并秉持创新承诺,期待与您联系。让我们携手合作,将您的工程挑战转化为价值增长和成功的机遇。欢迎立即联系我们进行交流。