-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

-

产品组合

查看所有产品Ansys致力于通过向学生提供免费的仿真工程软件来助力他们获得成功。

-

Ansys博客

July 19, 2023

减少芯片设计中的电迁移

从智能手机到笔记本电脑,我们每天所使用的各种设备的可靠运行都依赖于集成电路(IC)或芯片。这些芯片由大量的晶体管和互连器件组成,它们将电信号从芯片的一个部分传输到另一个部分。由于需要提高速度以及设计的复杂性——这会迫使更多的电能流向体积更小的器件,而这种集中的电流可能会降低芯片性能,就出现了被称为“电迁移”的现象。

什么是电迁移?

电迁移是由电流流动引起的原子运动。

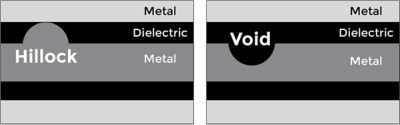

这种运动可通过形成空隙或小丘来改变导体的物理结构,从而导致短路、开路、性能劣化或设备故障。随着流经互连器件的电流密度增大,电迁移率也随之增加,这使得电迁移成为一个失控过程。事实上,电迁移是电路故障的主要原因。

图片:金属原子从某些区域向其它区域的电迁移,在半导体互连器件中形成的空隙和小丘

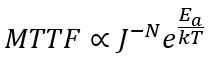

电流增大、温度升高、机械应力增加、导体存在缺陷以及杂质的存在都会加速电迁移。这些影响电迁移的因素可通过Black方程进行捕获——这是一种用平均故障时间(MTTF)来描述该现象的经验阿仑尼乌斯(Arrhenius)方程:

- J:电流密度

- N:比例因子

- k:玻尔兹曼常数

- T:温度(单位为开尔文)

- Ea:激活能(单位为焦耳)

Black方程由Robert Black于1969年提出,通过计算电迁移对设计的影响,帮助工程师了解电路的潜在使用寿命。该方程确定了MTTF与导线的电流密度、温度和材料属性的相关性。

电流密度:由于较大的导线具有更大的横截面面积,因此其电流密度较低,并且不易产生电迁移。

温度:随着温度升高,原子运动速度加快,从而增加了电迁移的可能性。

材料属性:某些材料具有更强的抗电迁移能力。例如,铜的高导电性使其成为比铝更受欢迎的选择。

随着我们的电子设备日益微型化,电迁移的概率及其引起的问题也显著增加。由于这些设备的可靠性能取决于芯片,因此必须减少电迁移,以保持产品的功能。

如何减轻芯片设计中的电迁移影响

为了避免电子组件中金属迁移所带来的失败和危险,芯片设计人员可以采用以下几种方法:

- 增加互连宽度,以降低电流密度。

- 使用具有高电迁移耐力的材料,如金和铜。

- 使用冗余通孔来分流电流强度。

- 减少互连器件之间的间距。

- 设计低电压水平的电路。

当然,解决芯片设计中的电迁移问题可能需要多种方法相结合。在为超大规模集成(VLSI)设计互连器件时,仿真软件是帮助您确定能够满足特定电流要求的理想选择。芯片设计人员必须分析流经互连器件的电流密度以及电阻增加的各种原因,以便预测芯片中的电迁移。

面对互连长度的增加以及宽度的减小、高电流密度和较差的散热能力,需要考虑非常复杂的电磁规则,以应对先进技术节点中的这些挑战。

芯片设计中的电迁移测试与监控

为了在芯片设计中实现可靠性,工程师必须在多种不同设计选择之间进行权衡。例如,增加互连宽度将减少电阻和电流密度,并增加电容。抑或选择减小互连器件之间的间距,这将有助于集成,但同时也会增加串扰耦合。

Ansys RedHawk-SC等仿真软件让芯片设计人员能够预测和分析互连器件的行为,以便在芯片投产之前确定系统内的功率分配。利用仿真来测试、验证和监控芯片设计,不仅可提升电子性能,还能帮助企业避免成本高昂的错误和产品召回。

成果:可靠的电子设备

电迁移是芯片设计和制造中的一大关键问题。虽然电迁移的影响可能是灾难性的,但可以通过一些措施来防止或最大限度减轻电迁移影响。通过优化互连器件的设计、选择合适的材料、控制温度和精心管理制造工艺,可以降低电迁移的风险。

随着电子产品的不断发展,了解并应对电迁移带来的挑战至关重要,以确保芯片的可靠性和使用寿命。利用Ansys Redhawk-SC和Ansys Totem等先进仿真签核工具,即使面对最紧凑的空间,工程师也能更快速构建更强大可靠的芯片系统。