-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

-

产品组合

查看所有产品Ansys致力于通过向学生提供免费的仿真工程软件来助力他们获得成功。

-

金属氧化物半导体场效应晶体管(MOSFET)栅极电阻是一个极其重要的参数,对于高频的先进半导体节点(16nm及更小)而言尤为重要。栅极电阻决定了MOSFET和互补金属氧化物半导体(CMOS)电路的许多特性,例如:

- 开关速度

- RC(电阻器-电容器)延迟

- Fmax—最高振荡频率

- 栅极(热)噪声

- MOS电容器和变容二极管(电压控制电容器)的串联电阻和品质因数

- 功率场效应晶体管(FET)的开关速度和均匀性

但是,由于寄生电阻、电容和电感等其他复杂因素,很难确定这些节点的实际栅极电阻值。寄生效应,是电路设计中由于设计版图和材料的物理缺陷而导致的不必要的电阻、电容或电感效应。顾名思义,寄生效应会导致功率损耗和发热,还会降低信号质量。为了更好地了解栅极的运行,很重要的一点是从模型中提取这些寄生效应,以获得实际的电阻、电容和电感值。

Ansys ParagonX集成电路版图寄生效应分析和调试软件等专业的电子设计自动化(EDA)工具,可用于通过可视化布局后网表的电阻-电容器(RC)网络连接来分析栅极电阻,这些网表包括SPEF(标准寄生交换格式,一种IEEE标准)和DSPF(国防安全原则框架)。这些工具可以探测网表,以查看和检查R和C值,并执行其他电气分析。SPICE模型也很有用,尽管寄生提取被认为是一种更准确的计算器件周围寄生R和C值的方法,因为它“了解”版图。

目前有许多关于栅极电阻的论文。然而,对于IC设计人员和版图工程师的实际工作而言,一些重要事项尚未得到讨论或解释:

- 寄生提取工具如何处理栅极电阻?

- 如何从版图或提取的布局后网表中评估栅极电阻?

- 如何确定栅极电阻是否受“固有”栅极电阻(栅极多晶硅)或栅极金属化布线的限制,以及最关键的层和多边形是什么?

- 工艺设计套件(PDK)的IC设计流程中是否考虑了栅极分布效应(单触点和双触点多晶硅的因数分别为1/3和1/12)?

- 晶圆代工厂PDK中是否考虑了垂直栅极电阻分量?

- 是否应使栅极变得更宽或更窄以降低栅极电阻?

在这里,我们将试图阐明这些未被讨论的问题,并为IC设计和版图工程师提供洞察信息,以更好地了解其设计中的栅极电阻。

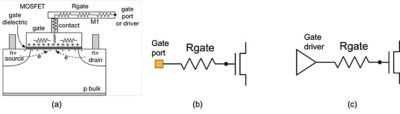

栅极电阻的定义和测量

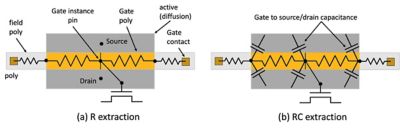

栅极电阻是从驱动点(即栅极端口或栅极驱动器)到MOSFET栅极实例引脚的“有效“电阻,如图1所示。实例引脚是SPICE模型的终端和电阻网络之间的连接点。

图1:MOSFET横截面和栅极电阻示意图

但是,图1中的简单示意图可能会产生误导。栅极网络可以非常大,包含许多驱动点、数十层(金属和通孔)、数百万个多边形和多达数百万个栅极实例引脚,如图2所示。

图2:MOSFET栅极网络顶视图和截面图的示意图

栅极网络是一种大型分布式系统,具有一个或多个驱动点和多个目标点。它的外观和行为就像一个庞大的常规时钟网络,负责将栅极电压分配给FET。为如此庞大而复杂的系统推导出有效的等效栅极电阻并不是一项简单而直接的任务。SPICE电路仿真不会明确报告栅极电阻值,这意味着需要寄生提取工具。

通过寄生提取工具处理栅极电阻

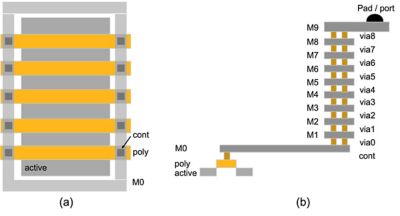

所有行业标准的寄生提取工具都能以类似的方式提取并处理栅极电阻。在版图中,MOS栅极结构由传统上被称为“poly”(多晶硅)的2D掩膜表示,尽管该材料可以由复杂的栅极金属堆叠组成,并且可能具有复杂的3D结构。

提取工具基本上会在与有源(扩散)层(图3中的深灰色阴影区域)相交处打破多晶硅的界限。这将把分析划分为两个部分:“栅极多晶硅”(有源区中的多晶硅;黄色阴影区域)和“场多晶硅(有源区外的多晶硅;浅灰色阴影区域)。多晶硅和有源区共同构成了晶体管。

图3:MOSFET栅极周围的R和RC提取

栅极多晶硅(黄色阴影区域)也在中心点断裂,MOSFET(SPICE模型)的栅极实例引脚连接到栅极多晶硅的中心点(黄色阴影区域中心的黑色垂直线)。栅极多晶硅由连接断裂点的两个寄生电阻器表示。用于表示场多晶硅的寄生电阻器连接到栅极触点或MEOL(中道工序,由互连金属/通孔组成)层,并进一步连接到上面的金属层。

栅极多晶硅与源/漏极扩散和触点之间的MOSFET外部寄生电容由寄生提取工具计算,并分配给电阻网络的节点。栅极电阻网络的寄生电容连接细节可能会对瞬态和AC响应产生重大影响,尤其是在栅极寄生电阻较大的先进节点中。

这些连接细节可以在DSPF文件中看到,但在开放文献或晶圆代工厂PDK文档中通常不会讨论,而DSPF文本文件的可视化检查非常繁琐,且需要专业知识。Ansys ParagonX等仿真软件可用于布局后网表(例如DSPF、SPEF)的RC网络连接可视化,检查R和C值,执行电气分析,以及执行其他有用的操作。

降阶栅极模型

MOSFET栅极沿栅极宽度形成大型分布式RC网络,如图4所示。

图4:沿栅极宽度分布的栅极属性和模型

这种分布式网络的AC和瞬态响应与包含一个R和一个C的简单集总电路不同。研究人员证明了,像这样的RC网络的行为与具有一个R和一个C单元的网络大致相同,1其中:

- C为总电容

- R=1/3 * W/L * rsh,用于单面连接的多晶硅

- R=1/12 * W/L * rsh,用于双面连接的多晶硅

这里,W是宽度,L是长度,rsh是多晶硅的方块电阻(Sheet Resistance)。系数1/3和1/12有效地为栅极实现了准确的降阶模型,将大量的R和C单元减少至两个(或三个)电阻器和一个电容器。使用降阶模型可简化并加速寄生提取软件的计算。

互连寄生对栅极电阻的影响

在较早的节点技术中,金属和通孔等金属互连的电阻非常低,而栅极电阻主要由栅极多晶硅控制,因此栅极电阻的分析和计算非常简单。

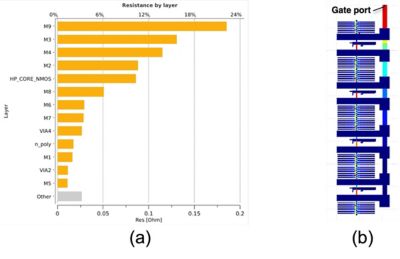

当技术达到16nm或更小特征尺寸时,互连具有非常高的电阻,并可显著增加(50%或更多)栅极电阻。根据版图的不同,栅极电阻可能主要来自任何层——器件(例如栅极多晶硅或场多晶硅)、MEOL、或BEOL(后道工序,由厚金属顶层和钝化层组成)。

图5显示了使用ParagonX软件进行栅极电阻仿真的结果。帕累托图(图5a)显示了每层的电阻贡献,有助于确定对于栅极电阻最重要的层。版图多边形布线(图5b)对栅极电阻的贡献可视化,能够立即表明栅极电阻的阻塞点或瓶颈,这对于指导版图优化工作非常有用。

图5:栅极电阻的仿真结果:(a)每层对栅极电阻的贡献;(b)在版图上用颜色显示多晶硅的贡献

FinFET中的栅极电阻

在平面MOSFET中,栅极具有非常简单的平面结构,并且栅极中的电流沿栅极宽度方向是一维的。

在鳍式场效应晶体管(FinFET)技术中,栅极封装在非常高的硅翅片上,从而形成复杂的3D结构。此外,会根据功函数(即将一个电子从固体内部刚刚移到固体表面外的真空点所需的最小热力学功)来选择栅极材料,以调整阈值电压。FinFET中的阈值电压不是由通道掺杂调节,而是由栅极材料进行调节。这些材料具有非常高的电阻,远高于请求的多晶硅(典型的方块电阻大约为10欧姆/sq)。此外,栅极可能由多个层构成,例如有硅片的界面层以及上面的一个或多个层。

但是,使用寄生提取软件时,所有这些细节是对IC设计人员和版图工程师隐藏的。他们通常可以看到“多晶硅”和“有源区”的多边形,这使得设计工作变得更加轻松。

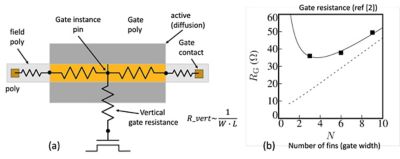

栅极电阻的垂直分量

在16nm之前的技术中,栅极电阻主要由横向阻抗控制。然而,在先进技术中,栅极材料层之间的多个界面会导致较大的垂直栅极电阻。该电阻与栅极多晶硅的面积成反比,其可以建模为一个附加电阻,将一个栅极实例引脚连接到栅极多晶硅的中心点,如图6a所示。因此,当栅极变得更窄(例如,翅片数量较少)时,栅极电阻会减少,但栅极电阻会在栅极宽度变得非常小时增加,如图6b所示。2它具有典型的非单调性。“较窄的栅极具有较低的栅极电阻”,这种旧的经验法则不再适用。因此,设计人员和版图工程师必须选择最佳(非最小)栅极宽度(翅片数量),以最大限度地减少栅极电阻。

图6:(a)考虑垂直栅极电阻的栅极模型,以及(b)测量和仿真的栅极电阻与翅片数量的关系(来自[2])

技术趋势

正如我们所看到的,随着技术扩展到越来越小的节点(目前低至2nm),栅极电阻和互连电阻都会显著增加——幅度高达一到两个数量级。因此,在较旧节点中对于栅极电阻并不重要的版图细节,在先进节点中变得非常重要。随着节点尺寸不断减小,这一趋势仍将继续。为了了解这些尺寸级别下的有效等效栅极电阻值,需要使用寄生提取软件(如ParagonX软件),因为SPICE模型在这些级别下不再有效。

欢迎进一步了解ParagonX软件,以改进您的IC设计流程。

参考资料

1.B. Razavi, et al., "Impact of distributed gate resistance on the performance of MOS devices," IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 41, pp. 750-754, 11 1994.

2.A.J.Sholten et al., "FinFET compact modelling for analogue and RF applications," IEDM 2010, p. 190.

Advantage博客

Ansys Advantage博客(The Advantage Blog)由Ansys专家和其他技术专家撰写,让您随时了解Ansys如何为创新赋能,推动人类踏上伟大征程。