-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

-

产品组合

查看所有产品Ansys致力于通过向学生提供免费的仿真工程软件来助力他们获得成功。

-

ANSYS BLOG

April 15, 2021

GLOBALFOUNDRIES携手Ansys加速硅光芯片设计

Ansys与全球领先的特殊工艺半导体制造商GLOBALFOUNDRIES(GF)展开合作,利用集成光子技术帮助解决数字世界的现实需求。

GF拥有高性能的单片集成硅光工艺解决方案,可以将RF CMOS与光子器件集成在同一个芯片上,实现更高的光电集成度,为数据中心和电信基础设施提供更高的带宽。

利用GF先进的硅光和封装技术,可以实现高性能的光互连,满足城际、长距离和数据中心的通信应用需求,同时最大化传输距离和能源效率。

Ansys拥有强大的Lumerical光子仿真工具,可帮助设计者理解并预测光在复杂结构、光路和系统中的特性,助力客户挖掘光子潜能,引领新技术和产品的开发。

Ansys和GF的最新合作提供了如下关键功能:1)基于工艺的自定义器件设计;2)基于Verilog-A的光电子系统仿真。这些功能支持精确的仿真结果,模型的兼容性,以及丰富的模型库。

工艺兼容的自定义器件设计

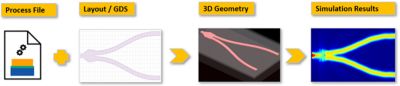

Ansys基于工艺的自定义器件设计流程帮助设计者在仿真和优化光子器件的过程中,时刻考虑到制造工艺,将设计版图和制造工艺通过 “工艺文件” 连接起来,产生工艺兼容的三维结构。

考虑到该功能对设计者的重要性,GF与Ansys联合首次推出针对GF硅光方案的工艺文件,用户现在可以更放心且更方便地进行设计,因为他们的Ansys Lumerical仿真符合GF关于层厚、材料等一系列规范。

利用GF的工艺文件,Ansys设计了一个与GF兼容的自定义Y-splitter,并进行了Lumerical FDTD仿真。如下图所示,通过工艺文件所产生的三维结构确保仿真与GF制造工艺兼容,用户无需手动地构建工艺的每一层并检查其准确性。

与工艺兼容的 Y-splitter在Lumerical FDTD中的仿真。通过版图和GF硅光工艺文件产生三维结构,使仿真与GF制造工艺兼容

光电子Verilog-A系统仿真

Verilog-A是一种常用的仿真CMOS电路紧凑模型的语言。随着与CMOS兼容的硅光技术的发展,人们也开始探索利用Verilog-A来进行光电混合仿真。然而,由于缺乏标准,光学Verilog-A的发展在业界相对支离破碎,导致不同机构提供的模型不兼容。

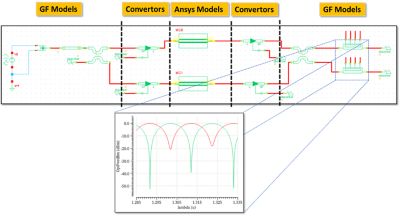

为了帮助设计者克服这项障碍,GF和Ansys联手,共同开发了Verilog-A转换器,使双方的光学Verilog-A模型兼容(业界首例)。用户现在可以在同一个光电系统中同时使用Ansys和GF的模型,还可以利用Lumerical CML Compiler自动产生任意自定义器件的紧凑模型(自定义器件可利用上述的与工艺兼容的器件设计流程)。

如下图所示,马赫泽德干涉仪是常用在光收发模块中的马赫泽德调制器的基础,设计者可在Ansys和GF模型之间添加了Verilog-A转换器,充分利用Ansys和GF提供的丰富的模型库,以及CML Compiler的自动模型生成功能,而无需自己编写Verilog-A代码。

综合利用Ansys和GF的Verilog-A模型仿真马赫泽德干涉仪,Verilog-A转换器使双方模型兼容

如欲了解更多Ansys基于工艺的设计流程,请观看Deliver Foundry-Compatible Custom Designs with Ansys’ New Process-Enabled Photonic Component Design Flow 网络研讨会点播视频。如欲了解更多Ansys光学Verilog-A平台和凑型建模功能,请浏览Ansys Lumerical应用库中提供的Verilog-A PAM4收发模块示例,并下载Lumerical CML Compiler的30天免费试用版。