THEMENDETAILS

Was ist Signalintegrität?

Die Signalintegrität (SI) eines Systems ist ein Maß dafür, wie viel sich ein elektrisches Signal zwischen dem Eintritt in einen Stromkreis und dem Austritt aus einem Stromkreis ändert. Bei digitaler Elektronik handelt es sich bei diesem Signal um einen elektrischen Strom, bei dem die Spannung im Zeitverlauf zwischen einem hohen und einem niedrigen Wert variiert.

Die Signalintegrität ist für jedes moderne elektronische System von grundlegender Bedeutung. Die Branche verwendet den Begriff „Integrität“, da er bedeutet, dass sie sich an einen Kodex hält, unbeeinträchtigt bleibt und vollständig und ungeteilt ist. Wenn die Signalform des Signals aufgrund von Übersprechen, Impedanzfehlanpassung und Verlusten erheblich vom Original abweicht, kann der Empfänger das Signal nicht lesen, was zu einem Problem mit der Signalintegrität führt. Aus diesem Grund ist die Signalintegritätstechnik – Analyse und Verbesserung von Problemen mit der Signalintegrität – ein wichtiger Bestandteil des Entwurfs von integrierten Schaltungen (ICs), IC-Paketen und Leiterplatten (PCB).

Die Erhöhung der Signalgeschwindigkeit und die Verringerung der Größe von Leiterplatten und Gehäusen machen die Handhabung von Problemen mit der Signalintegrität noch schwieriger. Digitale Hochgeschwindigkeitssignale und eine kleinere Geometrie verstärken Signalrauschen und Verzerrungen noch weiter. Mit zunehmender Herausforderung hat sich jedoch auch das Verständnis der Branche für den Umgang damit weiterentwickelt, ebenso wie die Möglichkeiten der Tools, die Ingenieur*innen zur Verfügung stehen, um ihre elektronischen Systeme zu definieren, zu simulieren und anzupassen.

Verzerrungen der Wellenform, Rauschen, zeitliche Verschiebungen und die Abnahme der Amplitude treten auf, wenn die Elektronen vom Treiber zum Empfänger fließen. Dies geschieht aufgrund des Widerstands im Material, des elektromagnetischen Feldes, das von den sich bewegenden Elektronen erzeugt wird, des von anderen elektromagnetischen Feldern induzierten Stroms und aufgrund der Kapazität des Stromkreises. Auf einer Leiterplatte wirken sich die Materialien, die Form der den Stromkreis bildenden Leiterbahnen, die Anordnung und Dicke der verschiedenen Schichten und die Art der Stromübertragung zwischen den Schichten auf diese Effekte aus.

Es ist auch wichtig, die in engem Zusammenhang stehenden Probleme zu erwähnen, die sich auf die Energieintegrität auswirken. Während die Signalintegrität die Signaltreue einer Leiterplatte bezeichnet, bezieht sich die Energieintegrität auf die Qualität der Energie, die den Komponenten, die diese Signale senden und empfangen, bereitgestellt wird. Die gleichen Probleme wie Impedanz, Induktivität und Dämpfung, die sich auf die Signalintegrität auswirken, spielen auch bei der Energieintegrität eine Rolle. Außerdem kann sich ihre Änderung gegenseitig negativ beeinflussen. Daher müssen Techniker*innen zur Verbesserung eines Layouts beide Aspekte simulieren und messen.

Warum ist die Signalintegrität so wichtig?

Wenn die Signalintegrität nicht berücksichtigt wird, können bei digitalen Geräten erhebliche Probleme auftreten. Das bedeutendste Problem tritt auf, wenn ein Signal so stark verzerrt wird, dass das über einen Stromkreis übertragene Signal für 0 oder 1 nicht korrekt empfangen wird und der Binärwert verfälscht wird. Außerdem kann das Gerät einer Störung unterliegen, wenn das Rauschen oder die Zeitverzögerung erheblich sind. In den hochkomplexen Leiterplatten von heute mit Hunderten von Leiterbahnen können Probleme mit der Signalintegrität auf nur einem Signalpfad schon dazu führen, dass die gesamte Leiterplatte unbrauchbar wird.

In der physikalischen Realität ist es unmöglich, ein Signal durch einen Stromkreis zu senden, ohne dass sich das Signal ändert, bis es am anderen Ende angelangt ist. Mit einem fundierten Verständnis der Grundlagen der Signalintegritätsanalyse, einem Gespür dafür, wie sich die SI auf das moderne Layout von Schaltungen auswirkt, und Methoden zur Erkennung und Bewältigung von Problemen mit der Signalintegrität können Layout-Teams die Signalintegrität über ihre Geräte hinweg minimieren und immer kleinere Formfaktoren und höhere Frequenzen erreichen.

Grundlagen der Analyse der Signalintegrität

Die physikalischen Gegebenheiten um die Elektronen auf ihrem Weg durch die Materialien beeinträchtigen die Integrität von Signalen. Die Gleichungen von Maxwell erfassen die Beziehung zwischen Ladung und Strom, wie Strom elektromagnetische Felder erzeugt und wie sich Felder auf den Strom auswirken.

Kurz gesagt wirken die Verbindungen in einer Leiterplatte, die so genannten Übertragungsleitungen für digitale Signale, wie Antennen, Widerstände und Kondensatoren. Die Eigenschaften des Signals, die Eigenschaften leitender und dielektrischer Materialien, die Geometrie und die relative Position der Schaltkreise und Schichten auf der Leiterplatte bestimmen die Größe und den Einfluss der in den Maxwell-Gleichungen beschriebenen physikalischen Beziehungen.

Die vier Problemtypen der Signalintegrität

Die oben erwähnten grundlegenden physikalischen Probleme mit der Signalintegrität lassen sich in die folgenden vier Kategorien einteilen:

1. Elektromagnetische Störungen (EMS)/Elektromagnetische Verträglichkeit (EMV)

In jedem Hochfrequenzkreis verwandelt die richtige Kombination aus Geometrie und Frequenz eine Leiterbahn oder eine Durchkontaktierung in eine Antenne, die ein Signal sendet, das sich auf andere Stromkreise auf der gleichen Leiterplatte oder in anderen Geräten, Steckverbindern oder Kabeln derselben oder nahe gelegenen Geräte koppeln kann. Wenn ein anderer Stromkreis Interferenzen empfängt, kann die Energie des elektromagnetischen Felds einen Strom induzieren, der zu Rauschen in diesem Signal führt. Die Übertragung elektromagnetischer Wellen verringert auch die Spannung des Signals, da die Erzeugung des Feldes Energie verbraucht. Designer*innen müssen die Störungen (EMS) minimieren und sicherstellen, dass das Gerät, das sie entwickeln, mit der elektromagnetischen Umgebung, in der es betrieben wird, verträglich ist (EMV).

2. Nebensprechen

Nebensprechen ist eine weitere Form der elektromagnetischen Interaktion. Es tritt auf, wenn das Signal in nahe aneinander gelegenen Hochgeschwindigkeits-Leiterbahnen ihre elektrischen und magnetischen Felder koppeln. Das unerwünschte Signal stammt von einer so genannten Störquellen-Leiterbahn, die mit dem Signal auf einer benachbarten Übertragungsleitung gekoppelt ist, der so genannten Störsenken-Leiterbahn. Es gibt folgende Kopplungsarten:

- Kapazitive Kopplung: Verursacht durch das elektrische Feld des Störquellenkreises, das eine Spannung im Störsenkenkreis induziert

- Induktive Kopplung: Verursacht durch das magnetische Feld des Störquellenkreises, das eine Spannung im Störsenkenkreis induziert

- Konduktive Kopplung: Verursacht durch den Strom beider Signale, der auf dem Rückweg in der Masseebene gekoppelt ist

3. Durch SSN (Simultaneous Switching Noise) verursachter Ground-Bounce

Ground-Bounce tritt auf, wenn die Signalmasse einer Leiterplatte nicht an allen Punkten gleich ist. Es handelt sich um ein Problem der Signalintegrität, das dadurch verursacht wird, dass mehrere Stromkreise gleichzeitig ihre Spannung zwischen ihrem hohen oder niedrigen Zustand ändern, was einen Spannungsanstieg in der Masseebene bewirkt. Dies führt dazu, dass die niedrige Spannung, die 0 in einem Binärsignal, höher ist als erwartet. Manchmal ist der Bounce so hoch, dass das Signal fälschlicherweise als hoher Zustand interpretiert wird.

4. Impedanzfehlanpassung

Leiterplatten-Designer*innen müssen die Impedanz von Wechselstromkreisen berücksichtigen. Die Impedanz ist der Widerstand gegen den Stromfluss und die Stromänderungen, die durch Induktivität und Kapazität verursacht werden. Eine Impedanzfehlanpassung tritt auf, wenn sich die Impedanz an einer beliebigen Stelle im Stromkreis ändert. Die Fehlanpassung bewirkt, dass ein Teil des Signals hin- und herreflektiert wird, bis es sich abschwächt. Neben der Entwicklung von Rauschen zum Signal kann eine Impedanzfehlanpassung zu einer Unsicherheit im Timing führen, die als Jitter bezeichnet wird. Ein Standardtool zur Bewertung von Impedanzfehlanpassungen ist die Zeitbereichsreflektometrie (TDR, Time-Domain Reflectometry). Die TDR misst die Reflexion in einer Übertragungsleitung.

Visualisieren der Signalintegrität mit einer Augendiagramm-Analyse

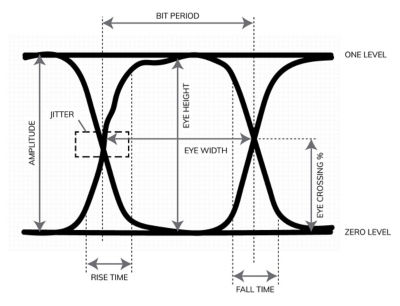

Die Augendiagramm-Analyse ist eines der am häufigsten verwendeten Tools zur Untersuchung der Signalintegrität. Ein Augendiagramm, auch Augenmuster genannt, ist eine Möglichkeit, das Verhalten eines digitalen Schaltkreises im Zeitverlauf zu betrachten. Ein sich wiederholendes Signal wird in den zu analysierenden Schaltkreis eingegeben, um das Ausgangssignal über einen bestimmten Zeitraum zu messen. Jedes Datenbit wird über das nächste gelagert, wobei die Zeit auf der X-Achse und die Amplitude auf der Y-Achse liegt. Da das Eingangssignal eine Rechteckwelle ist, würde eine perfekte Schaltung ein Bild erzeugen, das zwei horizontale Linien oben und unten und zwei vertikale Linien in der Mitte zeigt, die horizontal durch die Länge eines Datenbits und vertikal durch die Spannungsdifferenz im Signal getrennt sind.

Aber keine Schaltung ist perfekt, und daher entsteht eine Form, die wie ein Auge aussieht. Die oben beschriebenen Probleme der Signalintegrität zeigen sich als Verzerrung der geraden Linien. Die folgende Abbildung zeigt die typischen Werte, die Probleme in einem Stromkreis erkennen lassen. Werte wie Anstiegszeit, Abfallzeit, Jitter und augenkreuzende Prozentsätze zeigen, wie sich das Signal verzerrt und was das im System entstehende Rauschen mit dem Signal macht.

Durch den Vergleich von Augendiagrammen vor und nach einer Änderung der Leitungsführung, Geometrie oder des Materials können Designer*innen erkennen, wie die vorgenommenen Änderungen die Signalintegrität eines Schaltkreises verbessern.

Dieser analytische Ansatz wurde ursprünglich entwickelt, um die Signalintegrität eines Schaltkreises schnell mit einem Oszilloskop zu visualisieren. Heute verwenden Techniker*innen Augendiagramme, um die Leistung von Schaltkreisen auf Übereinstimmung mit der in einer Simulation vorhergesagten Leistung zu untersuchen. So können Designer*innen Änderungen schnell erkennen und die Auswirkungen erfassen, noch bevor ein Prototyp der Leiterplatte erstellt wird.

Signalintegrität und integrierte Schaltungen (ICs)

Dieser Artikel konzentriert sich auf die SI in Leiterplatten, aber auch die Signalintegrität in IC-Chips ist von entscheidender Bedeutung. Da die Strukturgrößen kleiner und die Datenraten sogar noch höher sind, ist der Aspekt der Signalintegrität bei der Auslegung integrierter Schaltkreise und der Definition von Verbindungen noch wichtiger. Kopplungseffekte durch das Schalten anderer Signale sind die Hauptursache für SI-Probleme in Chips. Außerdem befinden sich direkt außerhalb des Chips die Drähte, die als Verbindung zum Gehäuse dienen, so nahe, dass sie deutlich von Nebensprechen betroffen sein können.

Die Prototypenerstellung eines IC-Chips ist sehr schwierig. Daher werden Signalintegrität und Leistungsintegrität so früh wie möglich im Designprozess mithilfe von Simulationen modelliert, um potenzielle Probleme zu identifizieren und zu beheben. Mit diesen Hilfsmitteln werden die Chips überprüft, um vor Beginn des Fertigungsprozesses zu sehen, ob sie wie erwartet funktionieren.

Tipps zur Identifizierung von Problemen mit der Signalintegrität und zur Leistungsverbesserung

Die wichtigste Maßnahme, mit der Techniker*innen SI-Probleme bei digitalen Hochgeschwindigkeits-Designs vermeiden können, besteht darin, die etablierten Regeln für das Design von Leiterplatten einzuhalten. Hier einige der üblichen Regeln:

- Festlegen des Abstands zwischen Leiterbahnen

- Vermeidung abrupter Änderungen der Leiterbahnbreite

- Einhalten der zulässigen Eckradien

- Vermeidung von überstehenden Hülsen von Leiterbahnen und Durchkontaktierungen

- Vermeiden von Diskontinuitäten in der Grundebene, die die Rückkehrleitung unterbrechen

- Entwickeln von Differential Pairs mit gleicher Länge

- Verringern der Impedanz der Leistungsebene

- Strategische Platzierung der Grundebenen und die richtige Dicke jeder Schicht der Leiterplatte

- Vermeiden von Durchkontaktierungen für höhere Frequenzen

Selbst wenn alle Designregeln für die Leiterplattenlayouts eingehalten werden, können Probleme auftreten. Auch eine ausgeglichene Beachtung mehrerer Regeln, Fertigungseinschränkungen, Größenbeschränkungen und Kostenprobleme stellen eine Herausforderung dar. Gewöhnlich wird auf Simulationen zurückgegriffen, um diese Probleme zu identifizieren und Verbesserungen vorzunehmen.

Mit einem guten Parameter-Design und einem robusten Simulations-Toolset wie Ansys SIwave™ PCB, Elektromagnetik-Simulationssoftware-Pakete und die 3D-Hochfrequenzsimulationssoftware Ansys HFSS™ können Techniker*innen schnell Studien durchführen, um Lösungen zu bewerten.

Da ein elektromagnetisches Feld oder Strom in einer Leiterbahn nicht gesehen, gehört oder gefühlt werden kann, greifen Techniker*innen auf Simulationen zurück, um die auftretenden Felder und Flüsse zu visualisieren. Diese Visualisierung ermöglicht es, die Ausbreitung elektromagnetischer Felder zu betrachten, den Signalrückkehrweg zu sehen, die Erwärmung auf der Leiterplatte und unter Komponenten zu visualisieren und das Nebensprechen zwischen Leiterbahnpaaren zu bewerten.

Die Zukunft der Signalintegrität

Die Zukunft der SI ähnelt der jüngsten Vergangenheit: Weiter steigende Datenraten, steigende Taktgeschwindigkeiten und steigende Anforderungen an die Bandbreite. Die Gehäuse erfordern auch, für die Systeme kleinere Leiterplatten zu verwenden, mehr Komponenten auf diese Leiterplatten zu packen und die flexiblen Leiterplatten in verschlungene Formen zu biegen. Um den Anforderungen der Branche gerecht zu werden und Marktanteile zu steigern, werden Unternehmen neue Fertigungsprozesse einführen und mit verschiedenen Materialien experimentieren. Beides wirkt sich auf die Signalintegrität aus.

Ein weiterer Trend, der sich in naher Zukunft beschleunigen wird, ist die engere Integration von Layout und Simulation, wodurch mehr Physik im Designprozess in den Vordergrund gerückt wird. Bei der Entwicklung einer Strategie für eine Leiterplatte können Techniker*innen elektromagnetische Felder, die Integrität der Stromversorgung, die thermischen Eigenschaften und die mechanische Robustheit ihrer Layouts genau ergründen.

Ebenso wird auch die künstliche Intelligenz (KI) eine Rolle bei der Minimierung von Problemen mit der Signalintegrität spielen. Viele Layout-Tools verwenden bereits ältere Formen der KI, um Designregeln zur Führung von Leiterbahnen bei der Konvertierung von Schaltplänen in Leiterplattenlayouts umzusetzen. Die neue Generation generativer KI-Tools wird die Fähigkeiten dieser Tools sowohl für das Design als auch für die Simulation deutlich verbessern.