- Was Ist Advanced Semiconductor Packaging?

- Vorteile des Advanced Semiconductor Packaging

- Anwendungen für Geräte, die Module mit Advanced Semiconductor Packaging verwenden

- Advanced Packaging-Komponenten und -Technologien

- Herausforderungen beim Advanced Semiconductor Packaging

- Die Zukunft des Advanced Semiconductor Packaging

Was Ist Advanced Semiconductor Packaging?

Advanced Semiconductor Packaging beinhaltet eine Reihe von Herstellungsprozessen, die mehrere Halbleiterchips in einem einzigen Elektronikgehäuse kombinieren. Dieser Ansatz steigert die Leistungsfähigkeit und senkt den Stromverbrauch und die Kosten.

Traditionelles Packaging ist wie ein einstöckiges Gebäude auf einem Grundstück. Mit dem fortschrittlichen Packaging können Sie mehrere Gebäude auf einem kleineren Grundstück platzieren und diese mit Brücken, Schächten und Tunneln verbinden. Unternehmen, die diese Verfahren effektiv nutzen, können sich einen Wettbewerbsvorteil auf dem schnell wachsenden Halbleitermarkt verschaffen.

Die gängigsten Verfahren, die beim Advanced Packaging zum Einsatz kommen, sind 2.5D, 3D-IC, heterogene Integration, Fan-Out Wafer Level Packaging und System-in-Package. Jedes Verfahren ist eine andere Methode, einen einzelnen Chip von einem Wafer zu nehmen und ihn mit anderen in einer einzigen, elektrisch verbundenen Baugruppe zu platzieren, die von Kunststoff, Metall oder Glas umgeben ist. Dies ist das Gehäuse. Nach der Erstellung wird das Gehäuse mit einer Leiterplatte oder einem flexiblen Band verbunden und in ein elektronisches Gerät eingesetzt.

Vorteile des Advanced Semiconductor Packaging

Die Fähigkeit, immer mehr Transistoren auf weniger Raum unterzubringen, nimmt ab, da die Halbleitertechnologie allmählich an die Gesetze der Physik stößt. Jahrzehntelang hat sich die Mikroelektronikindustrie an der Vorhersage des Intel-Mitbegründers Gordon Moore orientiert, dass sich die Dichte der Transistoren in Chips alle zwei Jahre verdoppeln wird (Mooresches Gesetz), und hat ihre Investitionen und Planungen an diesem Tempo ausgerichtet. Das führte dazu, dass jede Generation von Chips immer kleiner und dichter wurde, wodurch die elektrischen Verbindungen in den Geräten zu einem Leistungsengpass wurden. .

Advanced Packaging ist eine gute Möglichkeit für Designer*innen diese Einschränkung zu überwinden. Damit lassen sich Engpässe beseitigen und Kosten senken, indem mehrere Chips in drei Dimensionen angeordnet und Verbindungen direkt zwischen Chips und in integrierten Übergangsschaltkreisen hergestellt werden. Ein weiterer Vorteil ist die Platzierung von Chips mit unterschiedlichen Funktionen in unmittelbarer Nähe, wodurch der Stromverbrauch gesenkt, die Geschwindigkeit gesteigert und Multifunktionsgeräte in einem einzigen Gehäuse vereinfacht werden.

Dieser Formfaktor eines einzigen Gehäuses senkt auch die Herstellungs-, Versand- und Lagerkosten, indem die Integration von einem Nachbearbeitungsschritt, der mehrere Komponenten umfasst, zu einem Front-End-Schritt am Standort der Halbleiterfertigung, auch Fab genannt, verlagert wird. Dieser Ansatz senkt zudem die Arbeitskosten für das Packaging erheblich, da an Standorten mit niedrigen Arbeitskosten keine separaten Packaging-Anlagen erforderlich sind.

Anwendungen für Geräte, die Module mit Advanced Semiconductor Packaging verwenden

Durch den wachsenden Bedarf an Rechenleistung und Speicherplatz für all die menschengemachten Daten entsteht eine größere Nachfrage nach effizienteren und kostengünstigeren mikroelektronischen Geräten. Anspruchsvollere und leistungsfähigere Unterhaltungselektronik schafft einen Markt für mehr Funktionalität in kleineren Gehäusen mit geringerem Stromverbrauch. Immer mehr Geräte werden intelligenter und enthalten Komponenten, die messen (Sensoren), Daten importieren, berechnen (Prozessoren), Daten speichern (Speicher) oder Daten exportieren. Advanced Packaging kann dazu beitragen, dass ein Produkt mehrere Instanzen jeder Funktion in einem einzigen Modul vereint.

Einer der am schnellsten wachsenden Bereiche ist hier die Automobilindustrie. Fortschrittliche Systeme für Leistung, Effizienz und Sicherheit in Verbindung mit einer immer größeren Anzahl von Sensoren steigern die Nachfrage nach robusteren, effizienteren und kostengünstigeren elektronischen Modulen mit fortschrittlichem Packaging.

Internet der Dinge (IoT)-Geräte sind ein weiteres Beispiel für den Wunsch von Produktdesigner*innen, mehrere elektronische Funktionen in einem einzigen Bauteil zu vereinen, um das elektronische Design zu ergänzen. Eine Lösung mit fortschrittlichem Packaging vereinfacht die Automatisierung bei der Montage und die Komplexität der Leiterplatte bei gleichzeitiger Steigerung der Leistung und Senkung der Kosten und des Energiebedarfs.

Advanced Packaging trägt dazu bei, die hohen Anforderungen an die Datenverarbeitung von künstlicher Intelligenz (KI) und High-Performance-Computing (HPC) zu erfüllen. Dieser Ansatz bietet mehr Funktionalität in einer kleineren, energiesparenden Konfiguration. Anbieter von Hardware für KI und HPC, wie NVIDIA, haben Lieferketten für fortschrittliches Packaging aufgebaut. Sie haben sich Intel und den Advanced Packaging-Fähigkeiten von TSMC zugewandt, um die Multifunktionsmodule herzustellen, die sie benötigen, um die Leistung zu steigern und gleichzeitig den Energiebedarf und die Kosten unter Kontrolle zu halten.

Advanced Packaging-Komponenten und -Technologien

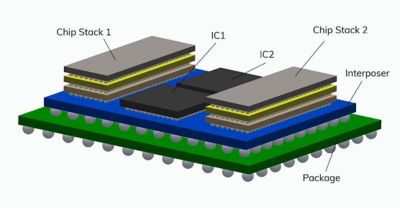

Das Advanced Semiconductor Packaging nutzt mehrere Technologien, um IC-Chips effizienter in einem Gehäuse zu kombinieren.

Ein guter Ausgangspunkt für das Verständnis von Advanced Packaging ist ein Blick auf die Komponenten und die unterschiedlichen Advanced Packaging-Technologien, die von Halbleiterherstellern eingesetzt werden.

Komponenten

- Chiplet: Ein ungepackter diskreter Die, der für eine bestimmte Funktion optimiert ist und mit anderen Chiplets und Multifunktions-IC-Chips auf Gehäuseebene kombiniert wird.

- Die:. Ein aus einem größeren Wafer ausgeschnittener Block aus Halbleitermaterial, der Schaltkreise enthält, die eine oder mehrere Funktionen ausführen können. Wenn diese Dies mit einem Substrat oder anderen Dies verbunden sind, werden sie zu einem Chip.

- E/A-Pads oder Bumps: Leitende Bereiche auf der Oberfläche eines Chips, die dazu dienen, Signale in oder aus dem Chip zu senden.

- Interconnect: Eine Struktur, die zwei oder mehr Schaltkreiselemente verbindet, um einen elektrischen Strom zwischen ihnen zu übertragen. Das ist normalerweise eine dünne Struktur, die eine oder mehrere Dies verbindet.

- Interposer: Eine Materialschicht zwischen einem oder mehreren Chips und einem Substrat. Beim Advanced Packaging kann dies ein Material auf Silizium- oder Glasbasis sein.

- Leiterplatte (PCB): Eine flache Struktur, die starr oder flexibel sein kann, mit mehrschichtigen Schaltkreisen, die die Komponenten in einem elektronischen System elektrisch verbinden. Sie werden normalerweise aus FR4 hergestellt, wenn sie starr sind, oder aus Polyamid, wenn sie flexibel sind.

- Redistribution Layer (RDL): Eine zusätzliche metallisierte Schicht unter einem oder mehreren Dies, die interne Leiterbahnen enthält, die für bessere E/A-Pads sorgen.

- Lötkugel: Eine kleine Lötkugel, die zum Verbinden von Komponenten in einem Halbleitergehäuse verwendet wird. Ihre Größe variiert je nach Verbindung.

- Substrat: Eine flache Komponente, die Schaltkreise enthält, die andere Komponenten in einem Gehäuse physisch und elektrisch verbinden. Ein IC-Substrat ist eine Schicht aus Halbleitermaterial und einem Laminatsubstrat aus FR4 oder Polyamid.

- System-on-Chip (SoC): Ein IC-Chip, der alle Computer- oder Elektronikfunktionen auf einem einzigen Chip integriert.

- Silizium-Durchkontaktierung (TSV): Eine elektrische Verbindung zwischen Ober- und Unterseite eines Siliziumwafers oder Dies. Dadurch wird ein dünnes Halbleitermaterial zu einer Verbindung zwischen den Komponenten.

- Drahtbindung: Ein Draht zwischen einem Die und einem Substrat oder zwischen mehreren Dies. Diese relativ kostengünstige Methode, Komponenten in einem Gehäuse zu verbinden, wird vorrangig beim herkömmlichen Packaging eingesetzt.

Technologien

2.5-D-Stapel nutzen einen Interposer mit TSVs, um mehrere Chips mit dem Gehäuse zu verbinden, und ein 3D-Stapel nutzt TSVs, die in die Dies integriert sind, um diese vertikal zu stapeln.

- 2.5-D: Anstatt mehrere Dies auf einem IC-Substrat zu befestigen, wird bei der 2.5-D-Technologie ein Interposer zwischen den Dies und dem Substrat eingesetzt. Der Interposer nutzt TSVs, um Signale durchzuleiten.

- 3D-IC: Eine Methode, bei der mehrere Dies übereinander gestapelt werden. Die Dies werden mit TSVs verbunden.

- Fan-Out Wafer-Level-Packaging: Ein RDL überträgt von dichten E/A-Pads auf dem Chip zu einer größeren Kugelgitteranordnung auf dem Substrat.

- System-in-Package (SiP): 2.5D- oder 3D-IC-Technologien werden dazu genutzt, ein komplettes Computer- oder Elektronikgerätegehäuse zu produzieren. Anstatt alle für eine SoC-Lösung benötigten ICs zu platzieren, kombiniert SiP mehrere Dies, um das gleiche Verhalten in einem einzigen Gehäuse zu erreichen.

Herausforderungen beim Advanced Semiconductor Packaging

Vom Packen eines Koffers bis hin zur Entwicklung der neuesten GPU-Module geht es beim Verpacken darum, alles, was Sie brauchen, so effizient wie möglich in Ihren Raum einzupassen. Bei fortschrittlichen Halbleiteranwendungen müssen Sie sich mit der Stromversorgungsintegrität, der Signalintegrität, der thermischen Integrität und der mechanischen Beanspruchung befassen und gleichzeitig die Kostenziele einhalten.

Interconnects

Jeder Chip in einem Gehäuse muss mit den E/A-Pads verbunden werden, die das Modul mit dem Rest des elektronischen Geräts verbinden. Leitende Pfade, wie Interconnects, TSVs oder Drähte, müssen in das Gehäuse integriert werden. Da sie ein Signal übertragen, muss jeder Pfad überprüft werden, um sicherzustellen, dass das Signal die Signale seiner Nachbarn nicht stört und sich nicht zu sehr erhitzt.

Energie

Die Energieeffizienz ist ein wichtiges Unterscheidungsmerkmal auf dem Markt. Kunden möchten mit weniger Energieaufwand mehr erreichen. Daher müssen Gehäusedesigner*innen Konfigurationen entwickeln und Technologien einsetzen, die den Stromverbrauch und die Verluste senken.

Wärme

Jede Komponente im Gehäuse kann Wärme erzeugen, wenn Spannung angelegt wird. Das Gehäuse benötigt Lösungen für das thermale Management, die eine Konfiguration und Materialien nutzen, die den Wärmestau minimieren, die Wärme von den Komponenten wegleiten und die Auswirkungen auf die verwendeten Geräte berücksichtigen.

Stabilität

Werkstoffe dehnen sich aus und ziehen sich zusammen, wenn sich ein Gehäuse erwärmt und wieder abkühlt. Die Designer*innen müssen unterschiedliche Werkstoffe und Verbindungstechnologien einsetzen, um sicherzustellen, dass die unterschiedliche Ausdehnung der einzelnen Werkstoffe und das wiederholte Wachsen und Schrumpfen nicht zu Ausfällen bei den Interconnects oder Chips führt. Zum Verständnis für die Ermüdung von Lötkugeln und das Gehäusedesign gehört auch die Beständigkeit in rauen Umgebungen bei Anwendungen in Fahrzeugen, IoT und Luft- und Raumfahrt.

Kosten

In der wettbewerbsintensiven Halbleiterfertigung sind die Kosten ein wichtiger Faktor. Das herkömmliche Packaging von Chips als Backend-Prozess kann arbeitsintensiv sein und Transportkosten beinhalten. Advanced Packaging-Prozesse müssen die Automatisierung nutzen und das Packaging zu einem Teil der vorgelagerten Prozesse machen, einschließlich integrierter Tests. Designer*innen nutzen häufig Optimierungstools, um ihre Optionen intelligent und kostenbewusst auszuloten.

Die Zukunft des Advanced Semiconductor Packaging

In der gesamten Halbleiter-Lieferkette entwickeln Unternehmen Pläne, die ein fortschrittlicheres Packaging, höhere Leistung und niedrigere Kosten vorsehen. Eine kürzlich von Yole Intelligence durchgeführte Studie hat ergeben, dass das Advanced Packaging im Jahr 2022 48 % zur 92 Milliarden Dollar schweren Branche beigetragen hat. Der Bericht prognostiziert, dass dieser Anteil bis 2028 auf 58 % einer 136 Milliarden Dollar schweren Branche anwachsen wird.

Das Packaging der nächsten Generation muss neue Materialien, eine stärkere Automatisierung und innovative Technologien einsetzen, um die steigende Nachfrage nach energieeffizienten und erschwinglichen Gehäusen, kompakteren Chipdesigns und System-in-Chip-Anwendungen zu erfüllen.

Der Wettbewerb im Packaging-Ökosystem zwischen Ländern und Unternehmen wird heftig sein. Das CHIPS-Gesetz von 2023 sieht 3 Milliarden Dollar an Mitteln für das amerikanische National Advanced Packaging Manufacturing Program vor. Die Branchenführer Intel, TSMC und Amkor haben Investitionen in Höhe von 3,5, 2,9 bzw. 2 Milliarden US-Dollar bis 2023 angekündigt, um neue Fertigungsanlagen für das Advanced Packaging zu entwickeln.

Abgesehen von den Technologien für die Fertigung sind die Techniker*innen auf der Suche nach besseren Softwaretools, die bestimmte Packaging-Technologien unterstützen und in den Design-Workflow integriert werden können. So haben Ansys, Microsoft und TSMC vor kurzem gemeinsam an einem cloudbasierten Stress-Simulationstoolset für das 2.5D/3D-IC-Packaging gearbeitet.