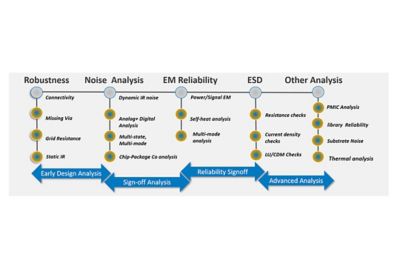

Ansys Totem is a transistor-level power noise and reliability analysis platform for comprehensive power integrity analysis on analog mixed-signal IP and full custom designs. Totem can create IP models for SoC-level signoff using RedHawk-SC. Totem analyses span early prototype to signoff and can handle a variety of design styles such as SerDes, data converters, power management IC, embedded memories, DRAM, Flash, FPGA, and image sensors. It analyses substrate noise, RDSON, self-heat, and ESD (with Ansys PathFinder™). Totem-SC’s cloud-native elastic compute architecture has the capacity to handle very large designs with modest memory overhead.