Overview

When validating and verifying embedded software, test engineers face several complex challenges. For instance, the standard for a DO-178C/DO-331 Level A application requires DC coverage of the model and MC/DC for the code. This activity may be demanding and require essential efforts.

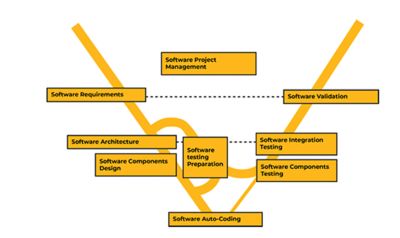

We propose an innovative V&V approach that enables you to significantly reduce effort while maintaining the same level of safety and compliance with DO-178C/DO-331.

The webinar will showcase our unique capability, low level test automatic generation. This innovative feature is sure to pique your interest and provide valuable insights into our approach.

We'll provide a demo of how we can help you reduce costs, speed certifications, and bring your products to the market faster.

What you will learn

- Effortless V&V: Significantly reduces the time and resources you invest in compliance

- Automatic Low-Level Test Generation: Automates the creation of low-level tests, streamlining your development process

- Quantifiable Savings: See real-world data on cost reductions and certification timeframes

- Live Demo: Get a firsthand look at how this can transform your V&V process and speed time to market

Who should attend

Everyone who works with DO-178/DO-331level A application, system architect, system design engineer, control engineer, software engineer

Speakers

Bernard Dion

John Macauley