Product Specs

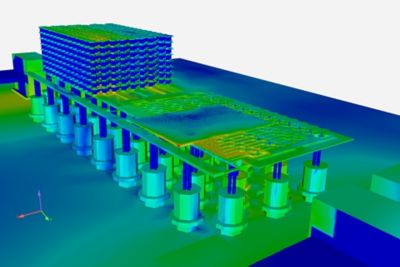

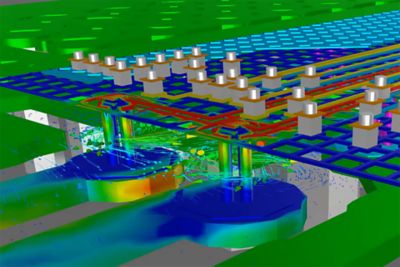

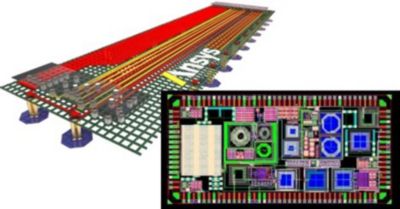

Manage the increasing complexity, multiphysics, cross-team collaboration, and integration requirements for electronic technologies such as RFICs, 3DICs, advanced packaging, and more. HFSS-IC breaks down silos and enables high-fidelity, high-performance IC-package systems co-design and co-simulation.