-

United States -

United Kingdom -

India -

France -

Deutschland -

Italia -

日本 -

대한민국 -

中国 -

台灣

-

Ansys stellt Studierenden auf dem Weg zum Erfolg die Simulationssoftware kostenlos zur Verfügung.

-

Ansys stellt Studierenden auf dem Weg zum Erfolg die Simulationssoftware kostenlos zur Verfügung.

-

Ansys stellt Studierenden auf dem Weg zum Erfolg die Simulationssoftware kostenlos zur Verfügung.

-

Kontakt -

Karriere -

Studierende und Akademiker*innen -

Für die Vereinigten Staaten und Kanada

+1 844,462 6797

ANSYS BLOG

April 8, 2019

Ensuring Electromagnetic Compatibility of Integrated Circuits for Automotive Applications

The automotive industry is adding a lot of electronic components into cars thanks to the electrification trend. Back in the year 2000, electronics accounted for 20 percent of a car’s production costs. Now, it can be as high as 30 to 35 percent. Some of these integrated circuits (IC) can help the car reduce emissions, avoid collisions or entertain passengers. Regardless of their function, these components must be compliant with electromagnetic compatibility (EMC) regulations.

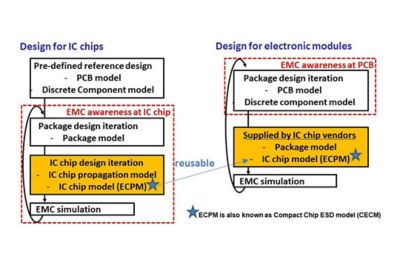

Electromagnetic susceptibility (EMS) simulation methodology using electrostatic discharge (ESD) models (part 1). (Source: 2018 DAC, professor Makoto Nagata of Kobe University described a design-for-EMS approach to on-chip ESD analysis.)

EMC refers to the interference electronic components can inflict on each other. Testing a component for its outgoing electromagnetic interference (EMI) involves determining its ability to produce electromagnetic (EM) emissions. Testing a component’s defense against EM emissions involves determining its EM susceptibility (EMS).

Think of it this way: The last thing anyone needs is an advanced driver-assistance system (ADAS) that malfunctions every time someone powers up an onboard entertainment system.

Engineers can use extended chip power models, generated by Ansys PathFinder, to assess the EM emissions and susceptibility of automotive electronic components — before creating a physical prototype. These models can represent:

- On-chip power delivery networks.

- Silicon substrate parasitic.

- Electrostatic discharge (ESD) devices.

How to Set Up Electromagnetic Compatibility Simulations

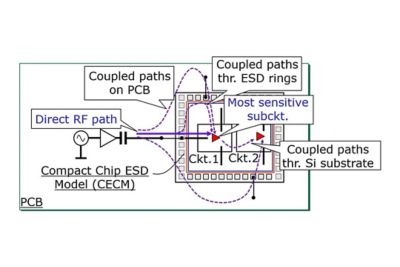

The EM emissions and susceptibility simulations must include all coupling paths for EM noise.

EMS simulation methodology using electrostatic discharge (ESD) models (part 2). (Source: 2018 DAC, professor Makoto Nagata of Kobe University described a design-for-EMS approach to on-chip ESD analysis.)

The simulations must also include any circuits, capacitors, resistors or devices that can contribute to, or be affected by, EM noise.

PathFinder’s system-on-chip (SoC) ESD models facilitate the inclusion of all the necessary components for EMC simulations. By using chip models and chip-package-board co-analysis, engineers can meet the strict EMC requirements of automotive ICs to ensure the safety and security of these applications.

In other words, engineers can use Ansys’ extended chip power models and chip-package-board co-analysis to ensure that a car’s entertainment unit won’t interfere with the functionality of an ADAS — or any other electronic component.

To learn how to leverage Ansys Pathfinder's chip power models in system-level EMC simulations, watch the webinar: Leveraging Chip Power Models for System-Level EMC Simulation of Automotive ICs.