- Che cos'è il packaging avanzato di semiconduttori?

- Vantaggi del packaging avanzato di semiconduttori

- Applicazioni per dispositivi che utilizzano moduli realizzati con il packaging avanzato di semiconduttori

- Componenti e tecnologie per il packaging avanzato

- Sfide nel packaging avanzato di semiconduttori

- Il futuro del packaging avanzato di semiconduttori

Che cos'è il packaging avanzato di semiconduttori?

Il packaging avanzato di semiconduttori è una raccolta di processi di produzione che combinano più chip di semiconduttori in un unico package elettronico. Questo criterio aumenta la capacità e riduce il consumo energetico e i costi.

Il packaging tradizionale equivale a costruire un edificio a un solo piano su un appezzamento di terreno. Il packaging avanzato consente di posizionare diversi edifici su un terreno più piccolo e di collegarli per mezzo di ponti, assi e tunnel. Le aziende che sfruttano efficacemente queste tecniche otterranno un vantaggio competitivo nel mercato in rapida crescita dei semiconduttori.

Le tecniche più comuni utilizzate nel packaging avanzato sono 2.5D, 3D-IC, l'integrazione eterogenea, il packaging a livello di wafer fan-out e il cosiddetto system-in-package. Ognuno rappresenta un modo diverso per estrarre un singolo chip da un wafer e posizionarlo con gli altri in un unico gruppo collegato elettricamente e circondato da plastica, metallo o vetro, appunto un package. Una volta creato, il package viene collegato a una scheda di circuiti stampati o a un nastro flessibile e collocato in un dispositivo elettronico.

Vantaggi del packaging avanzato di semiconduttori

La capacità di inserire più transistor in meno spazio sta rallentando man mano che la tecnologia dei semiconduttori inizia ad andare contro le leggi della fisica. Per decenni, l'industria microelettronica ha accettato la previsione del co-fondatore di Intel Gordon Moore secondo cui la densità dei transistor nei chip raddoppierà ogni due anni: la cosiddetta legge di Moore fu sviluppata proprio per guidare gli investimenti e organizzarsi per tenere il passo di questo ritmo. Ogni generazione di chip presenta quindi dimensioni più contenute e densità maggiori, tali da trasformare i collegamenti elettrici nei dispositivi in un collo di bottiglia per le prestazioni. .

Il packaging avanzato è un mezzo efficace che consente ai progettisti di superare questa limitazione. È possibile rimuovere i colli di bottiglia e ridurre i costi organizzando più chip su tre dimensioni e creando collegamenti direttamente tra i chip e nei circuiti integrati di transizione. Un ulteriore vantaggio è il posizionamento ravvicinato di chip con funzioni diverse, che riduce il consumo energetico, aumenta la velocità e semplifica i dispositivi multifunzione utilizzando un singolo package.

Questo fattore di forma basato su un unico package riduce anche i costi di produzione, spedizione e magazzinaggio, trasferendo l'integrazione da una fase di post-elaborazione che coinvolge più componenti a una fase front-end presso la sede di produzione dei semiconduttori (nota anche come fab). Questo metodo riduce inoltre in modo significativo i costi della manodopera per il packaging, eliminando la necessità di strutture di packaging separate in luoghi con costi della manodopera ridotti.

Applicazioni per dispositivi che utilizzano moduli realizzati con il packaging avanzato di semiconduttori

Con l'aumento della domanda della potenza di elaborazione e della memoria per archiviare tutti i dati creati dagli utenti, è necessario disporre di dispositivi microelettronici più efficienti ed economici. L'elettronica di consumo più sofisticata e capace crea un mercato per introdurre una maggiore funzionalità in package più piccoli con un minore consumo energetico. Sempre più dispositivi stanno diventando più intelligenti, aggiungendo componenti che misurano (sensori), importano dati, calcolano (processore), memorizzano dati (memoria) o esportano dati. Il packaging avanzato può aiutare un prodotto a combinare più istanze di ciascuna funzione in un unico modulo.

Una delle aree in più rapida crescita in questo settore è l'industria automobilistica. I sistemi avanzati in termini di prestazioni, efficienza e sicurezza, combinati con un numero sempre crescente di sensori, esigono moduli elettronici più robusti, efficienti ed economici realizzati con un packaging avanzato.

I dispositivi Internet of Things (IoT) sono un altro esempio del desiderio di un progettista di prodotti di combinare più funzioni elettroniche in un unico componente per aggiungerle al loro design elettronico. Una soluzione creata con un packaging avanzato semplifica l'automazione dell'assemblaggio e la complessità del circuito stampato, aumentando al contempo le prestazioni e riducendo i costi e le esigenze di alimentazione.

Il packaging avanzato aiuta a soddisfare le complesse esigenze di computing dell'intelligenza artificiale (AI) e dell'elaborazione ad alte prestazioni (HPC). Questa strategia assicura maggiori funzionalità in una configurazione più piccola e con un minore consumo di energia. I fornitori di hardware per l'AI e l'HPC, come NVIDIA, hanno stabilito catene di fornitura di packaging avanzati. Si sono rivolti ai servizi di packaging avanzato di Intel e TSMC per produrre i moduli multifunzione di cui hanno bisogno per aumentare le prestazioni mantenendo sotto controllo le esigenze di alimentazione e i costi.

Componenti e tecnologie per il packaging avanzato

Il packaging avanzato di semiconduttori utilizza molteplici tecnologie per combinare in modo più efficiente i chip IC in un unico contenitore.

Un buon punto di partenza per comprendere il packaging avanzato è quello di esaminare i suoi componenti e le varie tecnologie di packaging avanzato utilizzate dalle fonderie di semiconduttori.

Componenti

- Chiplet: un die dedicato senza packaging, ottimizzato per una determinata funzione e combinato con altri chiplet e chip IC multifunzione a livello di package.

- Die:. un blocco di materiale semiconduttore tagliato da un wafer più grande, che contiene circuiti progettati per eseguire una o più funzioni. Quando i die sono collegati a un substrato o ad altri die, diventano un chip.

- Pad o bump di I/O: aree conduttive sulla superficie di un chip utilizzate per inviare segnali in entrata o in uscita dal chip.

- Interconnessione: una struttura che collega due o più elementi del circuito per trasferire la corrente elettrica tra loro. Di solito è una struttura sottile che collega uno o più die.

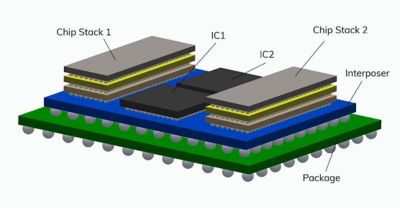

- Interposer: uno strato di materiale tra uno o più chip e un substrato. Nel packaging avanzato, il materiale può essere a base di silicio o vetro.

- Scheda di circuiti stampati (PCB): una struttura piatta, che può essere rigida o flessibile, con circuiti multistrato che collegano elettricamente i componenti in un sistema elettronico. Solitamente sono realizzati in FR4 se rigidi o in poliammide se flessibili.

- Strato di ridistribuzione (RDL): uno strato metallizzato aggiuntivo sotto uno o più die che contiene percorsi di conduzione interni che creano pad di I/O più vantaggiosi.

- Sfera di saldatura: una piccola sfera di saldatura utilizzata per collegare i componenti in un package di semiconduttori. Le sue dimensioni variano a seconda degli elementi da collegare.

- Substrato: un componente piatto contenente circuiti che collegano fisicamente ed elettricamente altri componenti in un package. Un substrato IC è uno strato di materiale semiconduttore con un substrato laminato realizzato in FR4 o poliammide.

- System-on-Chip (SoC): un chip IC che integra tutte le funzioni di un sistema informatico o elettronico in un unico chip.

- Through Silicon Via (TSV): un collegamento elettrico tra la parte superiore e la parte inferiore di un wafer o di un die di silicio. Trasforma un materiale semiconduttore sottile in un'interconnessione tra i componenti.

- Legatura metallica: un filo tra un die e un substrato o tra più die. Questo metodo relativamente economico di collegamento dei componenti in un package domina il packaging tradizionale.

Tecnologie

Gli stack 2,5-D utilizzano un interposer con TSV per collegare più chip al package, mentre uno stack 3D utilizza TSV progettati nei die per impilare i die verticalmente.

- 2.5-D: invece di collegare più die a un substrato IC, la tecnologia 2.5-D utilizza un interposer tra i die e il substrato. L'interposer utilizza i TSV per trasmettere i segnali attraverso l'interposer.

- 3D-IC: un metodo in cui più die sono impilati l'uno sull'altro. I die sono collegati da TSV.

- Packaging a livello di wafer fan-out: un RDL passa dai pad di I/O densi sul chip a una griglia a sfera più grande sul substrato.

- System-in-Package (SiP): le tecnologie 2.5D o 3D-IC vengono utilizzate per produrre un package completo per un dispositivo informatico o elettronico. Invece di posizionare tutti gli IC necessari per una soluzione SoC, SIP combina più die per ottenere lo stesso comportamento in un unico package.

Sfide nel packaging avanzato di semiconduttori

Dall'imballaggio di una valigia alla creazione dei più recenti moduli GPU, il packaging consiste nel riunire tutto ciò che serve in uno spazio nel modo più efficiente possibile. Per le applicazioni avanzate di semiconduttori, è necessario anche affrontare i problemi di integrità dell'alimentazione, integrità del segnale, integrità termica e sollecitazione meccanica, rispettando al contempo gli obiettivi di costo.

Interconnessioni

Ogni chip in un package deve essere collegato ai pad di I/O che collegano il modulo al resto del dispositivo elettronico. I percorsi conduttivi, quali interconnessioni, TSV o fili, devono essere progettati all'interno del package. Dal momento che trasportano un segnale, ogni percorso deve essere controllato per garantire l'assenza di interferenze con i segnali vicini ed evitare un eccessivo surriscaldamento.

Energia

L'efficienza energetica è un fattore di differenziazione sul mercato. I clienti vogliono fare di più con meno energia, quindi i progettisti di package devono sviluppare configurazioni e sfruttare tecnologie che riducono al minimo il consumo energetico e le perdite.

Calore

Ogni componente del package può generare calore quando viene applicata la corrente. Il package necessita di soluzioni di gestione termica che sfruttino la configurazione e di materiali in grado di ridurre al minimo l'accumulo di calore, allontanare il calore dai componenti e valutare il modo in cui influisce sui dispositivi utilizzati.

Robustezza

I materiali si espandono e si contraggono quando un package si riscalda e si raffredda. I progettisti devono utilizzare vari materiali e tecnologie di interconnessione per garantire la differenza di espansione per ciascun materiale e assicurare che la crescita e la contrazione ripetute non causano guasti in nessuna delle interconnessioni o dei chip. In termini di fatica della sfera di saldatura, il design del package deve resistere all'usura prodotta dagli ambienti difficili nelle applicazioni dei settori automobilistico, IoT e aerospaziale.

Costo

Nella competitiva industria dei semiconduttori, il costo è un fattore determinante. Come processo di back-end, il packaging tradizionale dei chip può essere laborioso e includere i costi di trasporto. I processi di packaging avanzato sfruttano l'automazione e spostano l'operazione di packaging, test integrati inclusi, tra i processi iniziali. I progettisti spesso utilizzano strumenti di ottimizzazioneper scegliere le opzioni in modo intelligente, tenendo conto dei costi.

Il futuro del packaging avanzato di semiconduttori

Lungo la supply chain dei semiconduttori, le aziende stanno sviluppando roadmap che includono packaging più avanzati, prestazioni più elevate e costi inferiori. Un recente studio di Yole Intelligence ha rivelato che nel 2022 il packaging avanzato rappresentava il 48% del settore da 92 miliardi di dollari. Il rapporto prevede che, entro il 2028, la quota crescerà fino al 58% di un settore da 136 miliardi di dollari.

La produzione di packaging di nuova generazione deve sfruttare nuovi materiali, una maggiore automazione e tecnologie innovative per soddisfare la crescente domanda di pacchetti efficienti dal punto di vista energetico e convenienti, design di chip più compatti e applicazioni system-in-chip.

La concorrenza nell'ecosistema del packaging tra paesi e aziende sarà intensa. La legge 2023 CHIPS Act prevede 3 miliardi di dollari in finanziamenti per il National Advanced Packaging Manufacturing Program. I leader del settore Intel, TSMC e Amkor hanno annunciato investimenti rispettivamente di 3,5, 2,9 e 2 miliardi di dollari nel 2023 per sviluppare nuove strutture di packaging avanzato.

Oltre alle tecnologie dell'impianto di produzione, gli ingegneri cercheranno strumenti software migliori che supportino specifiche tecnologie di packaging da integrare nel flusso di lavoro della progettazione. Ad esempio, Ansys, Microsoft e TSMC hanno recentemente collaborato a un set di strumenti di simulazione delle sollecitazioni basato su cloud per il packaging 2.5D/3D-IC.