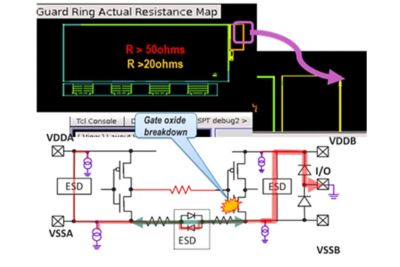

La riduzione delle tensioni di rottura dei dispositivi e delle dimensioni di interconnessione comporta un maggiore rischio di ESD nei processi inferiori a 16nm. Pathfinder-SC offre un'analisi completa degli eventi ESD on-chip, un requisito per tutti i progetti di chip.

La capacità di Pathfinder-SC di gestire design completi e il modello di utilizzo single-pass ottimizzato possono gestire simultaneamente centinaia di domini in un'unica analisi. Ciò è notevolmente più rapido rispetto agli approcci tradizionali, riducendo il tempo necessario per ottenere i risultati e riducendo il rischio di errori dovuti al partizionamento.

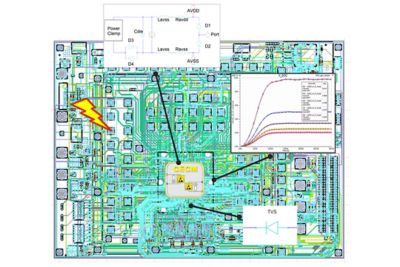

Qualsiasi problema rilevato può essere rapidamente sottoposto a debug con l'analisi basata sul layout di PathFinder-SC e la tecnologia Root cause Detection, risparmiando ancora una volta tempo e accelerando il time-to-market.

Pathfinder-SC include tutte le funzionalità in un unico prodotto: dall'estrazione RC alle simulazioni ESD, all'analisi delle cause di problematiche e alla fornitura di feedback sull'ottimizzazione. Include un estrattore RC integrato e non richiede licenze aggiuntive o strumenti esterni.

Pathfinder-SC è correlato al silicio da diversi clienti e convalidato da più fonderie che garantiscono precisione e riducono il rischio sul silicio.