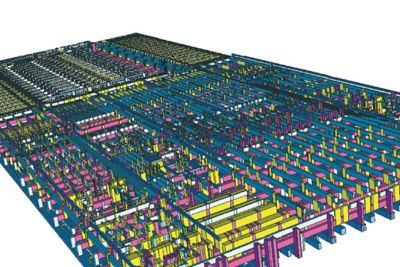

The proliferation of RF and high-speed circuits in modern silicon systems has raised electromagnetic coupling to a first order effect that must be accurately modeled to reliably achieve silicon success. But generating accurate parasitic models suitable for electromagnetic coupling analysis is far more complex than traditional RC extraction. And the size of these EM models has posed a challenge for simulators.

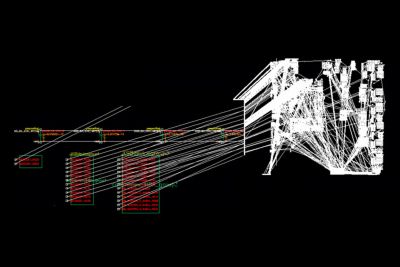

Exalto’s unprecedented capacity enables you to analyze extremely complex layouts with ease. Its unique netlist reduction methodology makes the output netlist extremely compact, mitigating any simulation issues. This makes it possible to thoroughly analyze complex EM interactions that were previously avoided through expensive over-design and guardbanding. The result is a smaller, cheaper design with more reliable performance characteristics.

Exalto enhances existing design flows by complementing regular extractor tools and interfacing seamlessly with all LVS tools.