簡要規格

Ansys Clock FX 會自動確認並模擬設計中所有時脈路徑,並可以說明在多種製程、電壓、溫度邊界和情境中每條路徑發生時脈抖動的所有關鍵因素。

產品系列

查看所有產品Ansys致力於為當今的學生打下成功的基礎,通過向學生提供免費的模擬工程軟體。

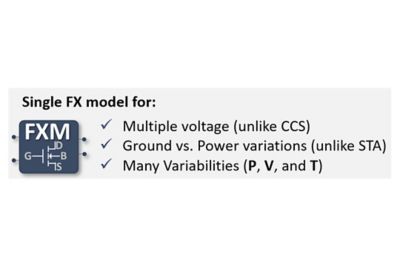

Ansys Clock FX 允許您計算完整 SoC 上含有變化的時脈抖動,無需使用任何捷徑。它獨特的單元模擬可使用單一材料庫為任何電壓或變化條件提供 SPICE 準確度時序。Clock FX 是具有完整執行緒的分散式結構,能夠擴充到數千個 CPU。

Ansys Clock FX 會自動確認並模擬設計中所有時脈路徑,並可以說明在多種製程、電壓、溫度邊界和情境中每條路徑發生時脈抖動的所有關鍵因素。

Ansys Clock FX 是現有簽核流程的附加元件,其效能足以評估 SoC 中所有時脈路徑中是否有時脈抖動,即使是最大的設計也沒問題。

Clock FX 對於延遲和抖動採用時脈路徑進行時序,可以自動確認和模擬設計中的每個時脈路徑。它說明多個製程、電壓、溫度邊界和情境中發生時脈抖動的所有關鍵因素。Clock FX 利用 SPICE 電晶體模型建立單一材料庫特性分析,使用完整的波形傳播來提供 SPICE 準確度,並且不使用捷徑即可正確分析所有變化性影響。

使用獨特的電壓、溫度和製程變化性感知單元建模進行的高容量 SPICE 層級時序:

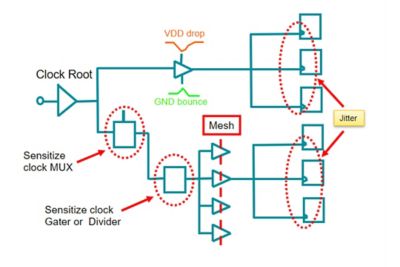

Ansys Clock FX 會在 RedHawk-SC 產生的時脈網路上挖掘動態電壓降,以使用 SPICE 級準確度計算時脈抖動。Clock FX 會說明準確的多電壓分析,並模擬供應變化對時脈路徑的延遲影響。

Ansys Clock FX 使用標準的單元模型或電晶體層級 SPICE 模型自動識別和模擬設計中的所有時脈路徑。其完整波形傳播提供所需的準確度,可在超低電壓下和進階製程中獲得可靠的結果。

Ansys Clock FX 分別處理電晶體層級的效應,例如電壓降和接地彈跳。這可以在容限極小且變化性極高的超低電壓下實現精確時序。

Ansys Clock FX 利用 SPICE 電晶體模型和完整波形傳播提供所需的準確度,可在在進階製程的超低電壓下獲得可靠結果。米勒電容和其他效應經過正確處理,且未使用捷徑。

Ansys Clock FX 為階層式且為分散式,與 Monte Carlo SPICE 相比,明顯減少返回時間和記憶體需求。

Ansys Clock FX 與 Ansys 簽核功率分析工具 RedHawk-SC 緊密整合,可獲得模擬所需的動態電壓降。它產生一系列豐富的抖動報告,包含各種抖動類型。

對 Ansys 而言,所有使用者皆能運用本公司產品非常重要,身心障礙者也不例外。因此,我們致力於遵循美國無障礙委員會 (第 508 節)、無障礙網頁內容規範 (WCAG)、自願性產品輔助工具範本 (VPAT) 當前格式等各項無障礙需求。

我們將在此解答您的問題,並期待與您交流互動。Ansys 的銷售團隊成員會立即與您聯絡。